| |

В. Бродин, А. Калинин, Л. Хохлов, И. Шагурин

Комплекс средств для обучения проектированию цифровых устройств на ПЛИС Altera с использованием системы Max+plusII

Прогресс микроэлектроники привёл к созданию программируемых пользователем логических интегральных схем (ПЛИС) с очень высокой степенью интеграции, применение которых, совместно с использованием современных микропроцессоров и микроконтроллеров, позволяет в короткие сроки выполнить разработку и начать производство электронной аппаратуры нового поколения [1,2]. Успехи в разработке ПЛИС позволили журналу в начале 1998 года сказать: “Прощайте, маленькие ASICs, да здравствуют FPGA” [3]. Причём слова о замене “маленьких” заказных микросхем следует воспринимать весьма условно — ведь степень интеграции современных ПЛИС типа FPGA достигает нескольких сотен тысяч эквивалентных вентилей. Таким образом, речь идёт о реализации на ПЛИС достаточно сложных цифровых систем (напомним, что микропроцессор Intel 386 содержал всего 275 тысяч вентилей).

Развитие ПЛИС существенно изменило задачи и возможности проектировщиков цифровой аппаратуры. Проектирование сложных цифровых устройств на классической базе — наборе простейших вентилей и триггеров, сохранилось только при реализации изделий в виде заказных микросхем, изготавливаемых на основе базовых матричных кристаллов или создаваемых из стандартных ячеек. Разработка таких устройств выполняется с помощью дорогостоящих систем автоматизированного проектирования (САПР СБИС), применение которых обеспечивает эффект в случае создания высокосложных изделий массового применения — микропроцессоров, микроконтроллеров, стандартных интерфейсных устройств и узлов телекоммуникационного оборудования. Для большинства электронных изделий малой и средней серийности наиболее перспективной является их реализация на базе ПЛИС, которые освободили проектировщиков от необходимости сборки разрабатываемых устройств из отдельных микросхем малой и средней степени интеграции (монтаж из “россыпи”). Можно с уверенностью сказать, что эффективное использование ПЛИС при разработке широкой номенклатуры цифровых устройств является непременным условием для достижения успеха в создании современной электронной аппаратуры.

Применение ПЛИС требует новых знаний и навыков от специалистов промышленности, а следовательно, и от преподавателей технических университетов и студентов. Новой становится технология проектирования цифровых устройств, центральное место в ней занимает описание проекта на языках высокого уровня типа HDL (Hardware Description Language), например, AHDL, VHDL и VerilogHDL. Процесс проектирования стал замкнутым в рамках одного класса инструментальных средств, поскольку появилась возможность исследовать проект с использованием редактора конфигурации микросхемы, функционального симулятора и временного анализатора.

Одним из наиболее известных производителей ПЛИС является фирма Altera. В качестве средства автоматизации проектирования устройств на основе собственных микросхем фирма Altera разработала систему MAX+plusII. Её продукция стала одним из стандартов “де-факто”, отличающимся высоким уровнем при невысокой цене микросхем ПЛИС и скромных требованиях к инструментальному ком-пьютеру (достаточно PC типа 486-DX4 с оперативной памятью от 16 Мбайт).

В лаборатории “Микропроцессорные системы” МИФИ на основе многолетнего опыта использования ПЛИС разработан комплекс средств для обучения проектированию цифровых устройств на ПЛИС Altera с использованием системы Max+plusII. Комплекс включает:

- методические материалы в виде описания лабораторного практикума;

- программное инструментальное обеспечение в виде системы MAX+plusII фирмы Altera. Пакет работает на персональных компьютерах в среде Windows, поставляется в виде дистрибутива на CD;

- аппаратное обеспечение в виде платы лабораторного макета и устройства типа ByteBlaster.

МИФИ имеет лицензию фирмы Altera на применение системы MAX+plusII в учебных целях.

Комплекс может быть установлен на отдельный компьютер для индивидуального обучения, а также на локальную сеть компьютеров учебного класса.

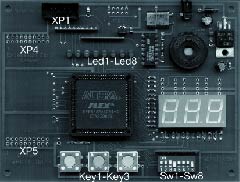

Рис. 1. Плата LabKit-8000

Лабораторный макет LabKit-8000 (рис. 1) реализован на базе ПЛИС типа EPF8282A широко распространённого семейства FLEX 8000 фирмы Altera. Эта ПЛИС содержит около 5000 эквивалентных вентилей, имеет 68 линий ввода/вывода. В реальных проектах может быть использовано до 2500 вентилей и свыше 200 триггеров, что вполне достаточно как для выполнения учебных заданий практикума, так и для практической работы специалистов. Кроме ПЛИС макет содержит устройства ввода и отображения данных, генератор тактовых импульсов частотой 4 МГц, звуковой пьезоизлучатель, стабилизатор напряжения питания. Дополнительные разъёмы (18 линий ввода/вывода) позволяют подключать к макету различные модули расширения. Предусмотрен также разъём для тестирования реализуемых устройств в соответствии со стандартом JTAG.

Конфигурация ПЛИС осуществляется с помощью персонального компьютера через кабель типа ByteBlaster, подключаемый к соответствующему разъёму макета. При выполнении практикума используется метод последовательной пассивной загрузки конфигурации от компьютера, на котором установлена система проектирования MAX+plusII. Технология внутрисистемного программирования ПЛИС позволяет реализовать на базе данного макета широкую номенклатуру комбинационных и последовательностных цифровых устройств различной сложности, проектирование и испытание которых производится в процессе выполнения лабораторных работ практикума. На макете предусмотрена также возможность подключения конфигурационного ПЗУ с последовательной выборкой для конфигурации ПЛИС без использования компьютера.

Разработанный практикум включает пять лабораторных работ.

Работа 1. “Графический ввод схемы устройства и функциональная симуляция с использованием САПР MAX+plusII”. В работе изучается графический редактор и осуществляется ввод в систему MAX+plusII принципиальной схемы комбинационного устройства, описанного булевым уравнением. После этого выполняется трансляция проекта, с помощью редактора логико-временных диаграмм формируется последовательность входных тестовых векторов и осуществляется симуляция (логическое моделирование). В результате система MAX+plusII формирует диаграмму состояний для выходов устройства, анализируя которую совместно с таблицей истинности, можно сделать заключение о правильности функционирования разработанного устройства.

Работа 2. “Описание схемы на языке AHDL, использование монитора иерархии проекта САПР MAX+plusII”. В этой работе изучается процесс описания цифрового устройства на языке AHDL и создание иерархического проекта. С помощью редактора Text Editor создаётся текстовый файл описания схемы на языке AHDL. Для ускорения процесса используются шаблоны конструкций языка, заложенные в систему MAX+plusII. Алгоритм программы реализуется с помощью оператора IF_THEN_ELSE. На основе текстового файла создаётся символьный файл, который с помощью редактора Graphic Editor включается в иерархический проект вместе с устройством, созданным в первой работе. Для анализа иерархического проекта используется монитор Hierarchy Display. После этого выполняется трансляция проекта, формирование тестовых векторов и симуляция в последовательности, аналогичной предыдущей работе.

Работа 3. “Разработка комбинационных схем, программирование ПЛИС и анализ размещения схемы на кристалле”. Работа посвящена проектированию комбинационных схем с использованием платы LabKit-8000, а также анализу и редактированию размещения схемы устройства на кристалле ПЛИС с помощью редактора конфигурации FloorPlan Editor системы MAX+plusII. Рассматривается функционирование схемы дешифратора для семисегментного индикатора и пример его описания на языке AHDL в виде таблицы. Перед трансляцией определяется тип микросхемы ПЛИС для реализации проекта и функции её выводов. После трансляции с помощью приложения Programmer осуществляется загрузка кода программы через ByteBlaster в ПЛИС на плате лабораторного макета LabKit-8000. Проверка работы дешифратора осуществляется вводом кода входных сигналов с переключателей и наблюдением знаков на семисегментном индикаторе. Для анализа размещения схемы устройства на кристалле используется редактор конфигурации FloorPlan Editor (рис. 2). С его помощью выполняется коррекция размещения выводов, после повторной трансляции работа дешифратора вновь проверяется с использованием платы LabKit-8000.

Рис. 2. Изображение конфигурации ПЛИС

Работа 4. “Разработка последовательностных схем, временной анализ в системе MAX+plusII”. В работе практически осваивается проектирование последовательностных схем на примере программируемого счётчика/таймера — типового узла современных микроконтроллеров. Особое внимание уделяется выполнению анализа временных характеристик разработанной схемы с помощью приложения Timing Analyzer, который производится после процедуры размещения и трассировки схемы на кристалле ПЛИС (рис. 3). При этом исследуется влияние размещения элементов и выводов на кристалле на быстродействие проектируемого последовательностного устройства.

Рис. 3. Результаты расчета быстродействия устройства

Работа 5. “Построение конечных автоматов (на примере арифметико-логического устройства RISC-микроконтроллера)”. В завершающей работе практикума проектирование сложных конечных автоматов изучается на примере регистрового АЛУ — ядра микропроцессорных и микроконтроллерных устройств. В процессе выполнения работы проектируется схема АЛУ, реализующего набор основных арифметических и логических операций, проверяется правильность их выполнения.

При выполнении практикума особое внимание уделяется самостоятельной работе. Следует отметить, что система MAX+plusII предоставляет пользователям широкие возможности её освоения с помощью опции Help (для её использования требуется, естественно, знание английского языка). Методика проведения работ предполагает сначала выполнение обязательного задания, реализация которого подробно описана в разработанном учебном пособии. Затем самостоятельно выполняется разработка индивидуального проекта. Для каждой работы предлагается набор, содержащий 10-20 заданий на проектирование типовых цифровых узлов и блоков: дешифраторов, компараторов, сумматоров, умножителей, регистров, счётчиков, генераторов кодов и других комбинационных и последовательностных схем. В устройствах, проектируемых по этим заданиям, используются размещённые на макете средства ввода и вывода данных: переключатели, кнопки, светодиоды, индикаторы, генератор импульсов, пьезоизлучатель. Таким образом обеспечивается наглядность результатов при функционировании разработанной схемы.

Данный практикум предполагается использовать как при обучении студентов соответствующих специальностей, так и для повышения квалификации специалистов промышленности.

При обучении студентов освоение методов реализации цифровых устройств на базе ПЛИС целесообразно проводить вместе с изучением классических методов проектирования. Будущие специалисты должны освоить основные способы преобразования и минимизации логических функций, научиться проектировать разнообразные устройства из набора серийно выпускаемых микросхем малой и средней степени интеграции или комплекта стандартных ячеек, используемых при разработке заказных БИС. Одновременно они должны научиться проектировать аналогичные устройства на базе ПЛИС, уметь провести сравнение технических и экономических характеристик устройств, реализуемых различными методами. Тогда в последующей деятельности они смогут обоснованно выбирать конструкторско-технологическую базу для выполнения своих проектов и находить оптимальные решения в соответствии с поставленными требованиями.

Для повышения квалификации специалистов промышленности, уже имеющих опыт разработки устройств на базе серийных микросхем, достаточно провести цикл практического освоения методики проектирования цифровых схем на базе ПЛИС с использованием данного лабораторного практикума. При этом теоретический раздел обучения может быть сокращён до одной вводной лекции, а основное внимание уделено практической реализации проектов на лабораторном макете. Длительность цикла обучения в этом случае может составить от 16 до 32 часов (3–6 дней) в зависимости от исходной подготовки специалиста. Предполагается организация таких циклов в МИФИ на платной основе. Достаточно подготовленные специалисты могут самостоятельно освоить методику проектирования цифровых устройств на базе ПЛИС Altera, используя разработанный лабораторный макет, учебное пособие и необходимое программное обеспечение.

Литература

- Шипулин С., Храпов В. Основные тенденции развития ПЛИС // Электронные компоненты. — 1996. — № 3-4. — С. 26–27.

- Стешенко В. Школа разработки аппаратуры цифровой обработки сигналов на ПЛИС. Занятие 1. Обзор элементной базы // Chip News. — 1999. — № 8. — С. 2–6.

- Прощайте, маленькие ASICs, да здравствуют FPGA // Chip News. — 1998. — № 2. — С. 23–25.

Тел.: (095) 362 7422

E-mail: pel@srv-vms.mpei.ac.ru

promel@mail.ru

|