|

|

|

|

|

| |

О.Стариков

Базовая схема, конструктивные блоки и шумовые характеристики ФАПЧ

синтезаторов частоты.

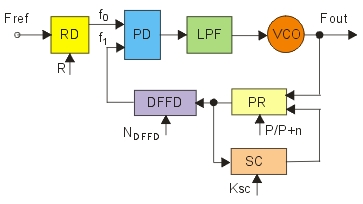

Рассмотрев в предыдущей статье базовую схему ФАПЧ и принцип ее функционирования,

теперь приступим к рассмотрению базовой схемы классического ФАПЧ синтезатора частоты,

которая представлена на рис.1.

Рис.1. Структурная схема однопетлевого ФАПЧ синтезатора частоты.

Ниже приведены выражения показывающие связь между опорной частотой, коэффициентами

деления счетчиков и выходной частотой.

Шаг сетки частот dF на выходе синтезатора можно рассчитать по формуле;

dF = fo n

Отсюда опорная частота после деления в опорном делителе должна быть;

fo = dF / n

Выражение для определения выходной (синтезируемой) частоты будет иметь вид;

Fout = fo P NDFFD + fo n Ksc

Шаг частоты на единицу кода NDFFD расчитывается, как;

dFDFFD = fo P

Коэффициент деления NDFFD (целое число без остатка) расчитывается по формуле;

NDFFD = Fout / (fo P)

Коэффициент деления поглощающего счетчика (т.е остаток от деления при вычислениии

кода NDFFD, деленный на минимальный шаг сетки частот) расчитывается, как;

Ksc = (Fout / (fo P) - NDFFD) / (n fo)

Так, как в качестве делителя PR используется прескалер с коэффициентами P/P+n, то при вычислении шага сетки частот dF можно заметить, что при использовании коэффициентов деления 20/22 и выше, значение шага сетки частот отличается от опорной частоты на значение nfo, а значение шага частоты на единицу кода NDFFD равно: dFDFFD = fo P или dFDFFD = (dF / n ) P , т.к. fo = dF / n, но так, как отношение P/n равно 10 (10/1, 20/2, 30/3, 40/4) получается, что: dFDFFD = 10 dF.

Т.е по сути мы имеем кольцевой делитель по модулю 10. С учетом вышесказанного и анализируя выражения (10) - (14) предыдущей статьи данного цикла, получим еще две формулы, которые отображают весь процесс синтезирования для данной базовой схемы:

Изменение коэффициентов деления DFFD происходит, согласно выражению: (NDFFD (P/n)),т.е всякий раз с каждым новым шагом настройки, на единицу изменяется все выражение в скобках, т.к мы имеем дело с кольцевым делителем. По другому можно записать:

(NDFFD x 10) + 1.

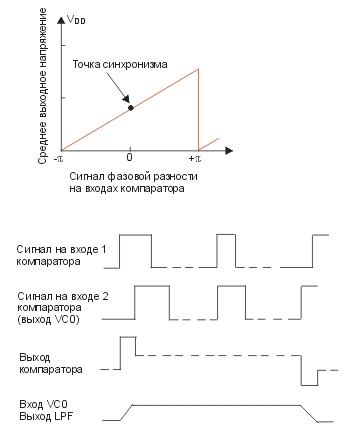

Рассмотрим теперь компоненты, на основе которых строится ФАПЧ синтезатор. Одним, из

важных узлов, является фазовый детектор, который может быть линейным и выполнен как

"четырехквадратный умножитель", или цифровым, выполненный на элементе "Исключающее -ИЛИ". Такой детектор работает с аналоговыми сигналами или с сигналами прямоугольной формы со скважностью 50%. Если на вход такого детектора подать прямоугольные импульсы, то зависимость его выходного напряжения от фазовой разности (при использовании фильтра нижних частот) будет иметь вид показанный на рис. 2.

Рис.2. Зависимость выходного напряжения от фазовой разности для детектора, выполненного на элементе "Исключающее - ИЛИ".

Детекторы вышеуказанного типа, обладают высокой линейностью и применяются в основном для синхронного детектирования сигналов. Для частотного синтеза сигналов детекторы этого типа мало подходят по причине повышенной остаточной пульсации, даже когда оба сигнала равны по фазе. Это вызывает периодические фазовые изменения, так называемую фазовую модуляцию, и повышенный уровень шума на выходе системы.

Существуют также другой тип детектора, который работает по фронтам прямоугольных

импульсов, и обладает чувствительностью только относительно расположения фронтов опорного сигнала и сигнала VCO. Детектор этого типа генерирует выходные импульсы

только тогда, когда появляется фазовая разность между опорным сигналом и сигналом VCO.

Эти импульсы по ширине равны промежутку времени между соответствующими фронтами

двух входных сигналов, и называются как, импульсы "опережения" или "отставания" во время

действия которых, схема источника тока либо "отводит", либо "отдает" ток. Во время же

отсутствия этих импульсов, выход фазового детектора находится в разомкнутом состоянии.

На рис.3. показана зависимость выходного напряжения от фазовой разности для такого детектора.

Рис. 3. Зависимость выходного напряжения от фазовой разности для детектора, работающего по фронтам прямоугольных импульсов

Конденсатор фильтра нижних частот является элементом запоминания напряжения, которое

поддерживает требуемую частоту настройки VCO. Об этом свойстве "памяти" мы говорили в первой части цикла, когда рассматривали контуры регулирования "первого" и "второго" порядка.

Т.е, при фазовой разности, фазовый детектор данного типа, генерирует последовательность импульсов, которые с выхода источника тока в виде управляющего напряжения соответствующей полярности, заряжают или разряжают конденсатор фильтра до напряжения синхронизма VCO и системы в целом. Поскольку, во время отсутствия импульсов рассогласования выход фазового детектора является разомкнутым (на практике все же возможен эффект дрейфа VCO или холостого хода), то и отсутствуют остаточные пульсации и фазовая модуляция, а соответственно уменьшается суммарный уровень шума системы.

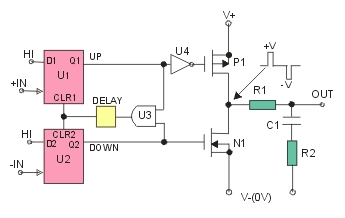

На рис.4 приведена принципиальная схема детектора, работающего по фронтам прямоугольных импульсов, выполненного на триггерах D - типа.

Рис. 4. Схема фазового детектора, состоящая из двух триггеров D - типа.

В этом устройстве, D - триггер запускается по положительным фронтам входных прямоугольных импульсов, и имеет следующие выходные состояния:

11 - оба выхода имеют высокое состояние, и подключены через схему AND (U3) назад ко входам CLR обоих триггеров.

00 - при таком состоянии выходов Q1 и Q2 оба транзистора P1 и N1 закрыты, и выход OUT имеет по существу высокий импенданс, т.е. разомкнутое состояние.

10 - при таком состоянии выходов, транзистор P1 открыт, а N1 закрыт и на выходе присутствует положительный потенциал источника питания.

01 - в этом случае транзистор P1 закрыт, а N1 открыт и на выходе присутствует отрицательный потенциал источника питания.

Элемент задержки DELAY включенный между выходом элемента U3 и входами CLR триггеров

препятствует дрейфу VCO и способствует более четкому вхождению системы в синхронизм.

Так, в момент времени, когда оба сигнала на входах +IN и -IN стремятся стать равными, процесс изменения выходной частоты VCO замедляется, в результате чего на выходе источника тока появляется некоторая ненулевая компонента сигнала, так называемые 'ни положительные - ни отрицательные" импульсы тока. Появление таких импульсов вызвало бы существенный дрейф VCO, в результате которого, снова появились бы или положительные или отрицательные импульсы рассогласования, и процесс снова бы повторился. Этот эффект циклической работы, вызвал бы появление на выходе источника тока модулированного сигнала, который являлся бы субгармоникой входной опорной частоты фазового детектора. Такой сигнал привел бы к очень существенным наводкам в выходном спектре VCO. Этот циклической эффект называют еще эффектом холостого хода, или люфта. С элементом задержки, даже когда оба входные сигналы равны по фазе, источником тока все еще будут генерироваться импульсы, которые не дадут VCO дрейфовать, и введут систему в синхронизм.

Кстати, необходимо заметить, что когда рассогласование на входах +IN и -IN существенное, то здесь, наоборот происходит быстрое изменение выходной частоты VCO. Сигнал рассогласования, поэтому является асиметричным и меняется более медленно в той части

цикла, где сигналы на входах +IN и -IN стремятся сравняться, и наоборот.

Последние замечания относительно элемента задержки и дрейфа VCO как раз объясняют

то, что теоретически, казалось бы при равенстве входных сигналов, выход фазового детектора

должен быть разомкнут, а практически возникает несколько другая неприятная ситуация, вызывающая этот самый дрейф. В зарубежной литературе, импульс формируемый элементом

задержки DELAY называют антилюфтовым широким импульсом (anti - backlash pulse width).

Контурный фильтр - это типичный фильтр нижних частот с так называемой характеристикой

"полюс - ноль". Передаточная характеристика фильтра зависит от величины (амплитуды) сигнала

источника тока, чувствительности VCO, коэффициента обратной связи системы регулирования

и от значения самой величины "полюс - ноль". Фильтр должен быть разработан так, чтобы

должным образом отслеживать изменения входной частоты, и с тем же обеспечивать уменьшение фазового шума на выходе системы. Для того, чтобы иметь приличный запас по фазе (обычно рекомендуется пороговое значение фазы p/4) в фильтр нижних частот последовательно с конденсатором включают резистор, чтобы приостановить спад характеристики на некоторой частоте. Отсечка частоты в 3-dB обычно называется шириной полосы пропускания контура Bw. Большая ширина полосы пропускания приводит к очень быстрой переходной характеристике, однако это не всегда выгодно, т.к. должен быть компромисс между быстрой переходной характеристикой и ослаблением паразитных составляющих системы.

Типовой расчет фильтра нижних частот и расчет общего коэффициента передачи контура

приведен в [3]. Также на сайте www.analog.com представлена программа расчета фильтра нижних частот "Loop Filter Design".

Опорный делитель RD, имеет, как правило, набор фиксированных коэффициентов деления

задаваемых программно, которые определяют значение опорной частоты. Значение опорной

частоты, находится обычно в диапазоне от нескольких десятков до сотен килогерц. В качестве

базового источника опорной частоты используют или кварцевый резонатор на несколько мегагерц (десятков мегагерц), или термостатированный генератор. Необходимо заметить, что стабильность частоты кварцевого резонатора или термостатированного генератора в большой степени (если не в основной), определяет стабильность всей системы в целом, т.к. опорная частота fo, по сути является эталонной. Создание высокостабильных термостатированных источников частоты является достатотчно ответственным делом, и требует отдельного разговора. Делитель с переменным коэффициентом деления DFFD также является программируемым, который задает отношение между входной и выходной частотами. Реализация такого делителя производится на основе счетчиков с разрядностью, определяемой максимальным коэффициентом деления. По сути, изменением коэффициента деления этого делителя мы изменяем значение выходной частоты.

Прескалер PR - это предварительный делитель частоты, который имеет двойной коэффициент деления. Эта структура возникла как решение проблемы, связанной с использованием достаточно высоких частот (от сотен МГц до нескольких ГГц) на выходе VCO.

Если такую частоту непосредственно подавать на вход делителя с переменным коэффициентом деления, то при опорной частоте равной 10 кГц и частоте VCO, скажем 1 ГГц, потребуется коэффициент деления порядка 100000, что в свою очередь потребует применения в качестве делителя с переменным коэффициентом деления по крайней мере 17- разрядного счетчика, который в добавок ко всему должен быть способен работать на данной входной частоте. Чтобы получать на выходе VCO такие достаточно высокие частоты и функционировать в этом диапазоне, перед делителем с переменным коэффициентом деления включают прескалер, который понижает выходную частоту до диапазона, в котором функционирует стандартная КМОП логика. Однако, при использовании двух модульного прескалера типа P/P+n в синтезаторе, выполненном согласно структурной схемы на рис.1, падает разрешающая способность системы (увеличивается шаг сетки частот), т.к. dF = fo n.

Если бы, в качестве предварительного делителя использовался простой прескалер с коэффициентом деления P, то dF было бы равно fo, а выходная частота опредялалась бы как:

Fout = fo P NDFFD + fo Ksc

На практике отношения значений Fout, fo, NDFFD и P стараются выбирать такими, чтобы

значение поглощающего счетчика было равно нулю (тогда его можно в принципе исключить из

схемы) и выходная частота для схемы простого прескалера будет определяться, как:

Fout = fo P NDFFD

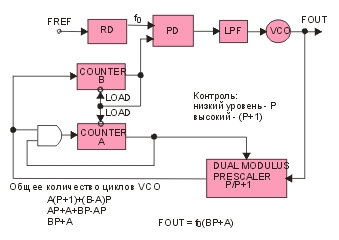

Структурная схема синтезатора изображенная на рис. 5, позволяет поддерживать выходную разрешающую способность системы, как fo, при использовании двух модульного прескалера,

c коэффициентами деления P/P+1.

Однако, здесь необходимо учитывать следующее:

1. Выходные сигналы обоих счетчиков находятся в высоком состоянии, если они (счетчики) "не определены", т.е. не подключены, и находятся в режиме ожидания. Подключение счетчиков происходит при определенной выходной частоте прескалера. (Об этом, будет рассказано в следующих статьях цикла, когда будет рассматриваться конкретная компонентная реализация).

2. Когда счетчик B подключен, его выход принимает низкое состояние, и разрешается загрузка обоих счетчиков новыми значениями.

3. Значение, загружаемое в счетчик B, должно быть всегда больше значения загружаемого в счетчик A.

Рис. 5. Структурная схема синтезатора частоты на базе двух модульного прескалера с поддержкой разрешающей способности системы.

Предположим, что счетчик В только что подключился, и в оба счетчика загружены новые значения А и В. Это позволяет найти количество циклов VCO, необходимых для того, чтобы привести его снова в состояние стабильности. Пока счетчик А не подключен, прескалер делит (уменьшает) частоту на P+1. Так, оба счетчика будут вести счет, уменьшая значения на 1, и каждый раз прескалер будет считать (P+1) циклов VCO. Таким образом, счетчик A будет подключен после ((P+1) x A) циклов VCO. В этот момент прескалер подключается к делителю P. Также, можно сказать, что в это время счетчик B все еще имеет (B - A) циклов перед тем, как переключиться в режим ожидания. Это будет до тех пор, пока получим состояние ((B - A) x P). Система теперь стремится назад к начальному условию, из которого мы ее запустили. Общее количество циклов VCO, необходимых для того, чтобы это случилось.

N = (A x (P +1)) + ((B - A) x P) = AP + A +BP - AP = A +BP

При использовании двух модульного прескалера необходимо учитывать самые низкие и самые высокие значения N. Эти значения должны быть такими, чтобы получить действительный диапазон, позволяющий изменять N с дискретным целым шагом.

Полагают, что выражение N = A + BP, гарантирующее непрерывное разнесение целого числа для N, должно быть в диапазоне от 0 до (P -1). Тогда, каждый раз увеличивая В, имеется достаточно разрешающей способности, чтобы заполнить все значения целого числа между ВР и (В+1) x Р. Как было уже отмечено выше, для функционирования двух модульного прескалера, значение В должно быть больше (или равно) А. Минимальное значение для N, имеющее способность к приращению в дискретных целых шагах, может быть получено как:

Nmin = (Bmin x P) +Amin = ((P - 1)) x P) + 0 = P? - P

а максимальное как:

Nmax = (Bmax x P) +Amax

В этом случае значения Amax и Bmax определяются разрядностью счетчиков A и B.

Следующим, достаточно важным узлом, является генератор управляемый напряжением - VCO. Развитию этой темы можно было бы посвятить не одну публикацию, т.к. это достаточно важное устройство, которое должно обеспечивать высокие характеристики по стабильности частоты, шумовым параметрам, не подвергаться самовозбуждению и генерировать спектрально чистый сигнал во всем частотном диапазоне. Проектирование и конструирование генераторов управляемых напряжением (как в прочем и других узлов ВЧ и СВЧ техники) требует хороших знаний и наличие практического опыта в высокочастотной схемотехнике. К счастью, в настоящее время существуют законченные модули VCO, которые обеспечивают хорошие характеристики для всевозможных применений. Такими примерами могут служить VCO 190-902T компании Vari - L (www.vari-L.com), MC1648 компании MOTOROLA (motorola.com), MQE520 - 1800 Murata, а также VCO таких производителей, как, Alps, Mini-Circuits, Z-Comm, Micronetics. Все вышеперечисленные элементы, входящие в состав ФАПЧ синтезаторов частот как правило выполняются в едином конструктивном исполнении (за исключением фильтра нижних частот и VCO) и представляют собой самостоятельный узел выполненный в виде интегральной схемы. Здесь необходимо однако оговориться по поводу отдельной реализации VCO, т.к. уже существуют однокристальные устройства реализующие в себе полный синтезатор с VCO и ряд дополнительных блоков. О таких устройствах для СВЧ применений говорилось уже на страницах журнала CHIP NEWS, в частности в №4 за 2001 год стр. 30 - 31, 48 - 49.

В заключении этой статьи хотелось бы уделить внимание важной для ФАПЧ систем теме - фазовому шуму. Существует так называемая, долгосрочная и краткосрочная стабильность частоты системы ФАПЧ и синтезаторов. Если долгосрочная характеризует стабильность частоты в течении длительного периода времени (часы, дни, недели), то краткосрочная стабильность характеризует изменения происходящие в течении секунд или долей секунд. Эти краткосрочные изменения могут быть случайными или периодическими, и представляют собой спектр со случайными и дискретными частотными составляющими, которые порождают широкие всплески и побочные пики в спектре выходного сигнала. Дискретные побочные составляющие вызваны тактовой частотой опорного источника сигнала, интерференцией линии питания и продуктами преобразования. Расширение, вызванное флуктуацией случайных помех называется фазовым шумом, и может являться следствием теплового, дробового и фликкер шума в активных и пассивных компонентах. К выходному сигналу VCO добавляется сигнал ошибки, значение которой определяется как средне - квадратичное значение фазовой флуктуации (погрешности фазы или колебания) и может быть выражено в пикосекундах или в градусах среднеквадратичного значения. Важно заметить, что полный выходной шум зависит от шума, вносимого каждым элементом схемы, т.е. от шума фазового детектора, источника тока, делителей, VCO, и может быть рассчитан, как шум подаваемый назад на вход фазового

детектора. Чтобы определить полный шум на выходе системы, необходимо все составляющие

представить в среднеквадратичном значении.

S2 = X2 + Y2 + Z2

где, S2 - полная мощность фазового шума на выходе системы;

X2 - мощность шума опорного делителя и делителей цепи обратной связи, подаваемая на входы фазового детектора;

Y2- мощность шума на выходе источника тока, обусловленная шумами от вышеперечисле - нных делителей и собственно, от шума самого фазового детектора и источника тока;

Z2 - мощность шума, вносимого VCO.

Необходимо вспомнить, что характеристика фильтра нижних частот с частотой среза на уровне 3 dB, обозначает ширину полосы пропускания контура Bw. Для частотных сдвигов на выходе меньше, чем Bw доминируют значения шума X и Y, а для частотных сдвигов намного больше, чем Bw доминируют значения фазового шума Z. Малое значение для Bw наиболее предпочтительно, т.к. позволяет минимизировать общее значение фазового шума, однако, может быть следствием медленного переходного процесса. Поэтому, определение ширины полосы пропускания должно зависеть от переходной характеристики и полной мощности интегрированного фазового шума.

Литература

1. Curtin M., O'Brien P. Phase-Locked Loops for High-Frequency Receivers and Transmitters - Part 2 Analog Dialogue 33 - 5 (1999).

2. Curtin M., O'Brien P. Phase-Locked Loops for High-Frequency Receivers and Transmitters - Part 3 Analog Dialogue 33 - 7 (1999).

3. Horowitz P., Hill W. The Art of Electronics, Second Edition, Cambridge University Press 1989.

4. SGS - THOMSON Microelectronics, Micropower Phase-Locked Loop, 1994.

|

|