| |

О. Стариков

Fractional-N и двойные Fractional-N/Integer-N синтезаторы частоты

Fractional-N синтезаторы частоты появились в большей степени как решение проблемы, связанной с увеличением скорости переключения частоты, снижением фазового шума вблизи несущей частоты и уменьшением уровня побочных составляющих в системе связи GSM (Global System for Mobile Communications) многоканального доступа, включая пакеты HSCSD (High-Speed Circuit Switched Data) и GPRS (General-Packet-Radio Service).

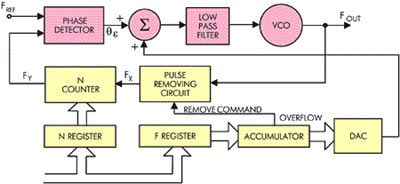

Наряду с Integer-N ФАПЧ-синтезаторами, с коэффициентом деления делителя в цепи обратной связи, устанавливаемом в виде целого (Integer) числа, существуют также Fractional-N синтезаторы частоты, у которых коэффициент деления в цепи обратной связи задаётся в виде дробного числа. Данный метод был разработан в начале 70-х годов, главным образом фирмами Hewlett-Packard и Racal, и носил название "digiphase", а впоследствии стал называться Fractional-N. Его появление обусловлено тем, что многие из разрабатываемых систем связи нуждались в быстром переключении частоты и более низком уровне фазового шума гетеродина. В классическом синтезаторе коэффициенты деления радиочастотного сигнала - только целые числа, что требует относительно низкой опорной частоты, которая, в свою очередь, определяет шаг перестройки (разнесение каналов) и нуждается в достаточно высоком значении коэффициента деления N в цепи обратной связи. Оба этих фактора достаточно сильно влияют на время регулирования и на фазовый шум системы в целом. Низкая опорная частота означает длительное время регулирования, а высокое значение коэффициента деления N - повышение фазового шума системы. Метод Fractional-N предполагает использование дробного деления в цепи обратной связи и уменьшение коэффициента деления N. В результате этого, можно использовать более высокую опорную частоту и всё ещё достигать необходимого разнесения каналов. Более высокая опорная частота означает, что уменьшится время регулирования системы (захват частоты будет происходить гораздо быстрее), а дробное деление в цепи обратной связи снизит соответственно фазовый шум системы. На рис. 1 показана структурная схема синтезатора, использующего Fractional-N метод.

Рисунок 1. Структурная схема синтезатора частоты типа Fractional-N

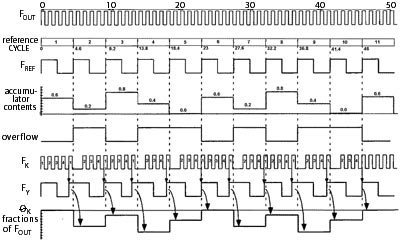

Данный метод предполагает производить поочерёдное деление дробных частей по длительности периода времени. Так, предположим, мы имеем коэффициент деления счётчика N в цепи обратной связи, равный 4,6. Теоретически, этот счётчик должен был бы отсчитывать 4,6 периода выходной частоты FOUT за определённое время, тем самым производя деление на 4,6, практически же это невозможно. По сути, мы должны произвести деление на 46, то есть отсчитать 46 периодов сигнала FOUT, в течение которых пройдёт 10 циклов (для данного случая) сигнала FREF. Дробная часть на каждом периоде сигнала FREF должна быть просуммирована в аккумуляторе, который представляет собой сигма-дельта модулятор. Более подробно этот процесс показан на временных диаграммах (рис. 2). В течение периода времени, необходимого для генерирования первого цикла сигнала FREF, счётчик N должен был бы отсчитать 4,6 периода выходной частоты FOUT. Как уже говорилось ранее, это невозможно. На самом деле будет отсчитано 4 периода FOUT и произведено деление на 4, а значение 0,6 будет отложено в аккумуляторе. Таким образом, в первом цикле будет недоставать 0,6 периода тактовой частоты FOUT. Здесь необходимо заметить, что в аккумулятор записывается тот же самый код, что и в регистр F. В начале второго цикла сигнала FREF счётчик N также будет производить деление на 4, и в аккумулятор к уже ранее записанному значению 0,6 добавится новое значение 0,6. Важной особенностью аккумулятора является то, что он может сохранять только значения меньше единицы, поэтому на втором цикле мы получим значение аккумулятора не 1,2 (как теоретически должно было быть), а 0,2, и уже это значение будет сохранено как содержимое аккумулятора. Таким образом, в начале каждого цикла в аккумулятор прибавляется содержимое регистра F к предварительно накопленному значению, и начиная с нулевой отметки времени, он будет "следить" за отсутствующими дробными частями. Начиная со второго цикла, с дополнительного выхода аккумулятора будет активизироваться сигнал переполнения OVERFLOW, который будет подаваться на второй вход схемы запрета, или удаления импульса PULSE REMOVING CIRCUIT. К началу второго цикла с выхода Fx этой схемы мы получим пять периодов тактовой частоты FOUT, так как переполнение, равное 1,2, даёт нам один дополнительный период импульса FOUT и сохранённое значение в аккумуляторе, равное 0,2. На рис. 2 эти импульсы показаны как 1 2 3 4 1, но уже в начале следующего, второго периода сигнал переполнения OVERFLOW будет блокировать прохождение первого импульса в этом цикле. С другого выхода аккумулятора сигнал переполнения будет поступать на вход ЦАП, с выхода которого уже аналоговый сигнал, пропорциональный по амплитуде значению переполнения, будет суммироваться в сумматоре S с сигналом ошибки фазового детектора. Тем самым будет сохраняться точность настройки VCO (генератора управляемого напряжением) с учётом дробных частей коэффициента деления N.

Рисунок 2. Временные диаграммы, показывающие процесс синтезирования с использованием Fractional-N метода

Из диаграммы видно, что аккумулятор имеет переполнение во 2-, 4-, 5-, 7-, 9- и 10-м циклах. Итак, последовательность из 10 циклов сигнала FREF будет содержать 6 переполнений, в результате которых получим общее количество периодов сигнала FOUT как (4x4) + (6x5) = 46. В итоге получим на выходе FY счётчика N последовательность импульсов с учётом добавочных периодов переполнения. С выхода FY эта последовательность импульсов будет поступать на второй вход фазового детектора с выхода, сигнал ошибки которого, с учётом сложения в сумматоре, будет поступать через ФНЧ на вход VCO, образуя тем самым контур ФАПЧ.

Fractional-N ФАПЧ-синтезаторы частоты, выпускаемые в настоящее время такими компаниями, как Analog Devices (ADI), Texas Instruments (TI) и Philips Semiconductors, представляют собой законченные устройства, способные работать на частотах до 3 ГГц. Существуют также двойные Fractional-N и Fractional-N/Integer-N ФАПЧ-синтезаторы частоты, имеющие два раздельных контура регулирования, и, как правило, Fractional-N секция работает в RF-контуре регулирования (RF - основная радиочастота), а Integer-N секция работает в IF-контуре регулирования (IF - промежуточная частота).

В табл. 1 приведены рабочие частоты Fractional-N и двойных Fractional-N/ Integer-N ФАПЧ-синтезаторов компании ADI.

Таблица 1. Рабочие частоты Fractional-N и Fractional-N/Integer-N ФАПЧ-синтезаторов частоты компании Analog Devices

| Устройство |

Частотный диапазон Integer-N |

Частотный диапазон Fractional-N |

Одиночный/ двойной |

Количество выводов |

| ADF4150 |

- |

Ј 550 МГц |

одиночный |

16 |

| ADF4151 |

- |

Ј 1,2 ГГц |

одиночный |

16 |

| ADF4152 |

- |

Ј 3,0 ГГц |

одиночный |

16 |

| ADF4156 |

- |

Ј 550 МГц |

одиночный |

20 |

| ADF4157 |

- |

Ј 1,2 ГГц |

одиночный |

20 |

| ADF4158 |

- |

Ј 3,0 ГГц |

одиночный |

20 |

| ADF4250 |

Ј 550 МГц |

Ј 1,2 ГГц |

двойной |

20 |

| ADF4251 |

Ј 550 МГц |

Ј 2,0 ГГц |

двойной |

20 |

| ADF4252 |

Ј 1,0 ГГц |

Ј 3,0 ГГц |

двойной |

20 |

| ADF4256 |

- |

Ј 550 МГц/

Ј 1,2 ГГц |

двойной |

20 |

| ADF4257 |

- |

Ј 550 МГц/

Ј 2,0 ГГц |

двойной |

20 |

| ADF4258 |

- |

Ј 1,0 МГц/

Ј 3,0 ГГц |

двойной |

20 |

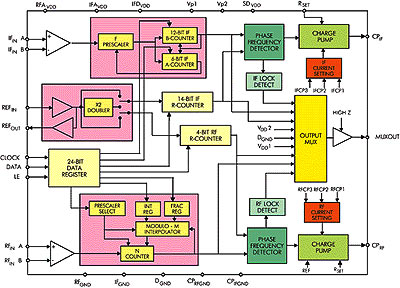

В качестве примера рассмотрим семейство ADF4250, ADF4251, ADF4252 двойных Fractional-N/Integer-N ФАПЧ-синтезаторов частоты, которые используются для построения гетеродинов с преобразованием верх и вниз по частоте, в базовых станциях и переносных трубках мобильной связи (GSM, CDMA, WCDMA, PCS, DCS), а также в LAN (локальных сетях), тестовом коммуникационном оборудовании и CATV (кабельном) оборудовании. Данные синтезаторы частоты состоят из двух раздельных IF- и RF-каналов. Канал IF реализован на базе Integer-N секции, а канал RF - на базе Fractional-N секции. Рабочие частоты каналов приведены в табл. 1. Эти микросхемы работают от источника питания в диапазоне от +2,7 до +3,3 В при среднем токе потребления 12 мА и, при необходимости, могут быть переведены в режим пониженного энергопотребления Power-Down. Программирование производится при помощи трёхпроводного последовательного интерфейса. Два программируемых двухмодульных прескалера (IF и RF) имеют коэффициенты деления:

IF: 8/9, 16/17, 32/33, 64/65;

RF: 4/5, 8/9.

Оба канала содержат программируемые источники тока и общий выходной мультиплексор. Fractional-N секция дополнительно содержит программируемый модуль-интерполятор и F-регистр. В принципе, данные ИМС во многом сходны по функционированию (за исключением Fractional-N секции) и программированию с ИМС серии ADF4110– ADF4113 ("Chip News" № 8 2001). Полная ФАПЧ для ИМС ADF4250, ADF4251, ADF4252 также может быть осуществлена при использовании внешнего фильтра нижних частот и VCO. На рис. 3 изображена функциональная схема ИМС семейства ADF4250- ADF4252. Из приведённой схемы видно, что канал IF имеет внутреннюю структуру, подобную структуре ИМС серии ADF4110– ADF4113, а соответственно похожий формат программирования регистров и представляет собой синтезатор частоты типа Integer-N. RF-канал представляет собой Fractional-N синтезатор. Регистры INT и F определяют коэффициент деления делителя N, который определяется из следующего соотношения:

N = (INT + (F/M)), (1)

где INT - значение целочисленного регистра, Integer; F - значение дробного регистра, Fractional; M - значение модуля-интерполятора.

Если в Integer-N синтезаторах коэффициент деления N в цепи обратной связи определялся как

RF/FPFD = N, (2)

где RF - частота на входе синтезатора (выходная частота VCO), FPFD - частота на входе фазового детектора, то в синтезаторах Fractional-N он будет определяться как

RF/FPFD = INT + (F/M). (3)

Так, для коэффициента деления, равного 4,6, пример которого описан выше и изображён на рис. 2, значение 4 мы должны загрузить в регистр INT, значение 6 - в регистр F, а в модуль-интерполятор должно быть занесено значение 10.

Исходя из этого, получим коэффициент деления

N = INT + (F/M) = 4 + (6/10) = 4,6.

Если, например, нам необходимо получить коэффициент деления, равный 40,6, получим следующее выражение:

N = INT + (F/M) = 40 + (6/10) = 40,6.

Формула для вычисления выходной частоты Fractional-N канала будет иметь вид:

FOUT = FPFD · (INT + (F/M)), (4)

где FOUT - выходная частота внешнего VCO; FPFD - частота на входе фазового детектора, которая, в свою очередь, будет определяться из выражения:

FPFD = REFIN · (1 + Doubler_en)/R, (5)

где REFIN - входная опорная частота; R - значение 4-разрядного опорного счётчика-делителя (для IF канала значение R будет 14-разрядным); Doubler_en - значение удвоителя частоты.

Так, если значение Doubler_en равно 0, то не будет происходить удвоения частоты REFIN, а частота FPFD будет равна REFIN (при условии, что R = 1). Если это значение равно 1, то будет происходить удвоение входной опорной частоты.

Рисунок 3. Функциональная схема Fractional-N/Integer-N ФАПЧ синтезаторов частоты ADF4250–ADF4252

Значения коэффициентов деления 8-разрядного регистра INT находятся в диапазоне от 1 до 255. Дробный регистр F является 12-разрядным, и значения его коэффициентов деления находятся в диапазоне от 1 до 4095. Модуль-интерполятор также 12-разрядный, и соответственно имеет такой же диапазон коэффициентов деления, как и регистр F. Важно также заметить, что F может принимать значение, равное 0, и должно быть меньше значения модуля-интерполятора M; существует некая зависимость 0 Ј F < M, показывающая эту взаимосвязь. Программирование регистров и режимов работы ИМС этого семейства, как было сказано выше, схоже с программированием ИМС семейства ADF4110–ADF4113. Некоторое отличие состоит в том, что ИМС семейства ADF4250–52 имеют большее число программных регистров, для выбора которых используются не два (как в ADF4110–13), а три последних младших бита С2, С1, С0 во входном сдвиговом регистре 24-BIT DATA REGISTER. Здесь используются семь программных регистров-защёлок:

- регистр-защёлка RF N DIVIDER REG программирует 8-разрядный INT- и 12-разрядный F-регистр;

- регистр-защёлка RF R DIVIDER REG программируетRF-прескалер, режим подключения или режим обхода удвоителя(DOUBLER) частоты опорного сигнала, 4-разрядный RF опорный счётчик-делитель и 12-разрядный модуль-интерполятор;

- защёлка инициализации RF INIT REG устанавливает ток и режим третьего состояния RF источника тока, поляризацию RF фазового детектора, режим RF Power-Down;

- регистр-защёлка IF N DIVIDER REG программирует IF-прескалер, 6-разрядный А и 12-разрядный В счётчики, а также установку или сброс бита усиления CP GAIN IF источника тока;

- регистр-защёлка IF R DIVIDER REG программирует 14-разрядный IF опорный счётчик-делитель, а также режим работы удвоителя DOUBLER;

- защёлка-инициализация IF INIT REG устанавливает ток и режим третьего состояния IF источника тока, поляризацию IF фазового детектора, режим IF Power-Down;

- MASTER REG программирует выход мультиплексора, общий режим Po-wer-Down, режим установки счётчика сброса COUNTER RESET, общий режим третьего состояния для источников тока.

В табл. 2–8 показан формат программирования этих регистров-защёлок.

Таблица 2. RF N DIVIDER REG

| Rese- rved |

8-BIT RF INT VALUE |

12-BIT RF FRAC VALUE |

Control bit |

| DB23 |

DB22 |

DB21 |

DB20 |

DB19 |

DB18 |

DB17 |

DB17 |

DB15 |

DB14 |

DB13 |

DB12 |

DB11 |

DB10 |

DB9 |

DB8 |

DB7 |

DB6 |

DB5 |

DB4 |

DB3 |

DB2 |

DB1 |

DB0 |

| P1 |

N8 |

N7 |

N6 |

N5 |

N4 |

N3 |

N2 |

N1 |

F12 |

F11 |

F10 |

F9 |

F8 |

F7 |

F6 |

F5 |

F4 |

F3 |

F2 |

F1 |

C3 (0) |

C2 (0) |

C1 (0) |

Таблица 3. RF R DIVIDER REG

| Presc aler |

RF Doub- ler BUP ASS |

4-BIT RF R Counter |

12-BIT Interpolator Modudlus |

Control Bits |

| DB20 |

DB19 |

DB18 |

DB17 |

DB16 |

DB15 |

DB14 |

DB13 |

DB12 |

DB11 |

DB10 |

DB9 |

DB8 |

DB7 |

DB6 |

DB5 |

DB4 |

DB3 |

DB2 |

DB1 |

DB0 |

| P3 |

P2 |

R4 |

R3 |

R2 |

R1 |

F12 |

F11 |

F10 |

F9 |

F8 |

F7 |

F6 |

F5 |

F4 |

F3 |

F2 |

F1 |

C3 (0) |

C2 (0) |

C1 (0) |

Таблица 4. RF INIT REG

| Reserved |

RF CP Current setting |

Rese- rved |

RF PD Pola- rity |

RF LDP |

RF Power Down |

RF CP3 State |

RF Coun- ter Reset |

Control Bits |

| DB15 |

DB14 |

DB13 |

DB12 |

DB11 |

DB10 |

DB9 |

DB8 |

DB7 |

DB6 |

DB5 |

DB4 |

DB3 |

DB2 |

DB1 |

DB0 |

| T5 |

T4 |

T3 |

T2 |

T1 |

CP2 |

CP1 |

0 |

P8 |

P7 |

P6 |

P5 |

P4 |

C3 (0) |

C2 (0) |

C1 (0) |

Таблица 5. IF N DIVIDER REG

| IF CP Gain |

IF Presc- aler |

12-BIT IF B Counter |

6-BIT IF A Counter |

Control Bits |

| DB23 |

DB22 |

DB21 |

DB20 |

DB19 |

DB18 |

DB17 |

DB16 |

DB15 |

DB14 |

DB13 |

DB12 |

DB11 |

DB10 |

DB9 |

DB8 |

DB7 |

DB6 |

DB5 |

DB4 |

DB3 |

DB2 |

DB1 |

DB0 |

| P15 |

P14 |

P13 |

B12 |

B11 |

B10 |

B9 |

B8 |

B7 |

B6 |

B5 |

B4 |

B3 |

B2 |

B1 |

A6 |

A5 |

A4 |

A3 |

A2 |

A1 |

C3 (1) |

C2 (0) |

C1 (0) |

Таблица 6. IF R DIVIDER REG

| IF Dou- bler |

15-BIT IF R Counter |

Control Bits |

| BYP- ASS |

DB17 |

DB16 |

DB15 |

DB14 |

DB13 |

DB12 |

DB11 |

DB10 |

DB9 |

DB8 |

DB7 |

DB6 |

DB5 |

DB4 |

DB3 |

DB2 |

DB1 |

DB0 |

| DB18 |

R15 |

R14 |

R13 |

R12 |

R11 |

R10 |

R9 |

R8 |

R7 |

R6 |

R5 |

R4 |

R3 |

R2 |

R1 |

C3 (1) |

C2 (0) |

C1 (1) |

Таблица 7. IF INIT REG

| Reserved |

IF CP Current setting |

IF PD |

IF LDP |

IF Power Down |

IF CP3 State |

IF Coun- ter Re- set |

Control Bits |

| DB15 |

DB14 |

DB13 |

DB12 |

DB11 |

DB10 |

DB9 |

DB8 |

Pola- rity |

DB6 |

DB5 |

DB4 |

DB3 |

DB2 |

DB1 |

DB0 |

| T10 |

T9 |

T8 |

T7 |

T6 |

CP3 |

CP2 |

CP1 |

DB7 |

P20 |

P19 |

P18 |

P17 |

C3 (1) |

C2 (1) |

C1 (0) |

Таблица 8. MASTER REG

| MIXOUT |

XOE |

Power Down |

CP3 State |

Counter Reset |

Control Bits |

| DB10 |

DB9 |

DB8 |

DB7 |

DB6 |

DB5 |

DB4 |

DB3 |

DB2 |

DB1 |

DB0 |

| M4 |

M3 |

M2 |

M1 |

P12 |

P11 |

P10 |

P9 |

C3 (0) |

C2 (1) |

C1 (1) |

Далее хотелось бы сделать некоторые сравнения Integer-N и Fractional-N синтезаторов. Возьмём вариант применения их в стандарте GSM-900, где частота между соседними каналами равна 200 кГц. Так, чтобы в Integer-N синтезаторе получить частоту на входе фазового детектора (после деления в цепи обратной связи), равную 200 кГц. При FOUT, равной 900 МГц, коэффициент делителя N должен быть равен 4500. На следующем шаге, чтобы получить выходную частоту 900,2 МГц, коэффициент деления N должен быть равен 4501. Как уже говорилось в начале статьи, большой коэффициент деления в цепи обратной связи является причиной увеличения фазовых шумов, а относительно низкая частота сравнения - причиной увеличения времени регулирования системы.

Сущность Fractional-N метода показывают выражения RF/FPFD = INT + (F/M) и 0 Ј F < M, приведённые выше, поэтому в Fractional-N синтезаторах частота фазового детектора FPFD (частота сравнения) может быть больше, чем разрешающая способность канала. Рассмотрим также вариант применения Frac-tional-N синтезаторов в GSM-900.

Для примера, зададимся следующими значениями:

FOUT = 900 МГц (первоначальное значение);

FPFD= 2 МГц;

разрешающая способность канала равна 200 кГц.

Значение модуля-интерполятора М будет равно 10, так как М = 2 МГц / 0,2 МГц (FPFD, делённая на шаг частоты между каналами).

В регистр INT должно быть загружено значение, равное 450 (900 МГц / 2 МГц). В регистр F на данном шаге должно быть загружено значение, равное 0. Используя формулу FOUT = FPFD x (INT + (F/M)), проверим, что для данных установочных значений выходная частота будет равна 900 МГц:

FOUT = 2 МГц · (450 + (0/10)) = 900 МГц.

Для следующего шага мы должны значение F увеличить на единицу, то есть коэффициент деления в цепи обратной связи теперь будет равен 450,1, и выходная частота:

FOUTT = 2 МГц · (450 + (1/10) = 2 МГц · 450,1 = 900,2 МГц.

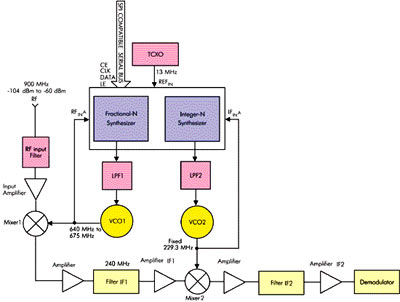

Это соответствует разрешающей способности RF-канала для GSM-900. Между значением коэффициента деления, равным 450, и значением 450,1, должно пройти 10 циклов частоты FPFD. На рис. 4 показан пример построения приёмной части базовой станции GSM-900 на основе двойного Fractional-N/Integer-N синтезатора частоты семейства ADF4250–ADF4252.

Рисунок 4. Приёмная часть базовой станции GSM-900

Эта базовая станция имеет диапазон Tx (передачи) от 925 до 960 МГц и диапазон Rx (приёма) от 880 до 915 МГц.

Мобильная телефонная трубка имеет, соответственно диапазон Tx от 880 до 915 МГц и диапазон Rx от 925 до 960 МГц. Рассмотрим приёмную часть базовой станции. В данной системе имеется 124 канала (8 пользователей на канал) с шириной 200 кГц. Полная ширина полосы - 24,8 МГц. Входной RF-сигнал частотой 900 MГц (выбрана средняя частота Rx-диапазона) через входной фильтр (RF Input Filter) поступает на входной усилитель (Input Amplifier) и далее подаётся на вход первого смесителя (Mixer1). На другой вход этого смесителя подаётся сигнал частоты настройки от генератора управляемого напряжением (VCO1), выполняющего функцию гетеродина настройки. Гетеродин настройки RF-канала реализован на Fractional-N cинтезаторе с внешним фильтром нижних частот (LPF1) и внешним VCO1. Таким образом, система должна сканировать входные частоты диапазона для поиска активных каналов. Так как первая промежуточная частота (IF1) равна 240 МГц, то VCO1 должен иметь диапазон выходных частот от 640 до 675 МГц, чтобы перекрывать Rx-диапазон. Когда опорная частота выбрана равной 200 кГц, выходное значение полной частоты VCO1 должно изменяться с шагом 200 кГц. Например, когда выходная частота VCO1 равна 650 МГц, базовая станция работает на приём в RF-канале частотой 890 MГц.

Для перехода на вторую промежуточную частоту (IF2) и демодуляцию сигнала, используем Integer-N синтезатор, который в комбинации с внешними LPF2 и VCO2 формирует фиксированную частоту 229,3 МГц. Во втором смесителе (Mixer2) происходит второе преобразование частоты, выделение фильтром Filter IF2 промежуточной частоты IF2, равной 10,7 МГц, и демодуляция сигнала. Выбор Fractional-N синтезатора в RF-канале обусловлен, как было сказано ранее, меньшим уровнем фазовых шумов и более высокой скоростью регулирования системы.

Fractional-N метод изначально предполагает уменьшение времени регу-лирования системы. Так, для ИМС ADF4252 время вхождения в захват может быть менее 100 мкс, а для ИМС семейства ADF4110 - 200 мкс и более (необходимо конечно учитывать установочные параметры систем при проведении измерений). Уменьшение времени регулирования достигается за счёт увеличения частоты сравнения в фазовом детекторе.

Дробное деление в цепи обратной связи и уменьшение значения коэффициента деления N снижает соответственно фазовый шум системы.

В любом случае, ИМС этих семейств (и Integer-N, и Fractional-N) обладают достаточно высокими характеристиками, чтобы использоваться во многих приложениях связи и телекоммуникаций.

Литература:

- ADF4250 - ADF4252 Fractional-N Freq-uency Synthesizers. Preliminary Data Sheet. Analog Devices Inc. Norwood. MA. 2001.

- Brendan Daly. Comparing Integer-N and Fractional-N Synthesizers. Microwaves & RF, 2001.

- Mark Curtin, Paul O’Brien. Phase-Locked Loops for High-Frequency Re-ceivers and Transmitters–Part 3. Analog Dialogue 33-7 (1999).

|