В. Стешенко, Р. Загидуллин, С. Карутин

Анализ сигналов и систем. Пакет SystemView компании Elanix. Занятие 3. Моделирование элементов радиоприемных устройств

Модель кольца ФАПЧ

В большинстве современных радиоэлектронных устройствах присутствуют схемы слежения за входным сигналом, причём в большинстве своём эти схемы цифровые и программно реализуемые, поэтому представляется интересным рассмотрение процесса расчёта и моделирования таких схем в SystemView. Рассмотрим процесс моделирования на примере схемы фазовой автоподстройки частоты (ФАПЧ) 2-го порядка.

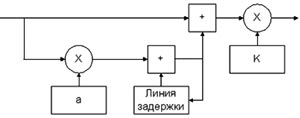

Обобщённая схема системы автоподстройки частоты имеет вид, представленный на рис. 1.

Рисунок 1. Общий вид схемы автоподстройки частоты

Как известно [1,2], схема слежения характеризуется коэффициентом передачи замкнутой цепи регулирования, для ФАПЧ в операторной форме он имеет вид:

(1) (1)

где K - коэффициент усиления, Sфд - крутизна характеристики фазового детектора (ФД), Sуг - крутизна характеристики управляемого генератора (УГ), F(p) - передаточная функция фильтра.

Коэффициент передачи связан с эквивалентной шумовой полосой системы связаны следующим соотношением:

(2) (2)

Задаваясь порядком астатизма системы 2, мы выбираем для кольца фильтр первого порядка. Реализация фильтра первого порядка и усилителя приведена на рис. 2.

Рисунок 2. Фильтр первого порядка и усилитель

Передаточная функция фильтра имеет вид

(3) (3)

где a - коэффициент фильтра, t - период следования отсчётов.

Подставляя (3) в (1), можно получить выражение для коэффициента передачи замкнутого кольца:

(4) (4)

Задавшись полосой и предполагая систему устойчивой по фазе с запасом в 45º, можно получить из (2) следующие выражения для коэффициента усиления K и фильтра a:

(5) (5)

a = 2 ·  fЭ · fЭ ·  1 1

где Sуг = 2p В/Гц, Sуг = 1 рад/с/В.

Для тактовой частоты 400 Гц, эквивалентной шумовой полосы фильтра 10 Гц и указанных выше значений крутизны получаем, что K = 1,59155 и a = 0,025.

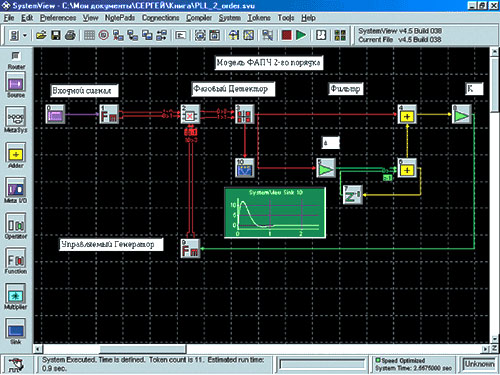

Внешний вид модели приведён на рис. 3.

Рисунок 3. Модель ФАПЧ 2-го порядка в SystemView

|

Блок №

|

Вид

|

|

|

0

|

|

|

|

1

|

|

|

|

2

|

|

|

|

3

|

|

|

|

5

|

|

|

|

6

|

|

|

|

7

|

|

|

|

8

|

|

|

|

9

|

|

|

|

10

|

|

|

Входной сигнал моделируется с помощью блоков {0} и {1}. Блок 0 задаёт скорость перестройки входной частоты и выбирается из библиотеки Source группы Aperiodic в виде функции Step Fct. В поле Amplitude можно задать скорость измерения частоты в Герцах (например 10 Гц), остальные параметры оставить без изменений. Генерация входного сигнала осуществляется блоком 1, являющимся FM Function библиотеки Function группы Phase/Freq, в поле Frequency задаётся начальное значение частоты входного сигнала в Герцах (например 100 Гц), в поле Phase - начальная фаза в градусах (например 45). Если необходимо задать перестройку входной частоты, то в поле Mod Gain необходимо занести значение, отличное от нуля (например 1).

Синфазная и квадратурная составляющая входного сигнала и сигнала УГ (блок 9) поступают на вход ФД, реализованного в виде перемножителя {2} и функции вычисления arctg {3} Блок 2 является функцией перемножения двух комплексных чисел Complex Multiplier из библиотеки Function группы Complex. Перемножение входного сигнала и на комплексно-сопряженный сигнал УГ реализуется установкой переключателя Multiply Type в положение Conjugate. Блок 3 возвращает значение arctg в радианах и реализуется в виде функции Four Quadrant ArcTangent библиотеки Function группы Functions. Модуль позволяет выполнять спрямление фазы, в случае если сигнал выходит за границы ±p, установкой переключателя Unwrap Output Phase в положение Unwrap.

С выхода ФД сигнал поступает на фильтр, реализуемый в виде двух сумматоров 4 и 5, усилителя 5 и линии задержки 6. Коэффициент a реализован в виде усилителя Gain {5} из библиотеки Operator группы Gain/Scale, установив в поле Gain значение коэффициента а, рассчитанного по формуле (5), (в нашем случае 0,025) и переключатель Gain Units в положение Linear. Интегратор фильтра реализован в виде сумматора Adder {6} и линии задержки Sample Delay Operator {7} из библиотеки Operator группы Delays. Установив в поле Delay значение 1, определим задержку на один такт. В поле Initial condition задаётся начальное состояние - нулевое.

Блок Gain {8} из библиотеки Operator группы Gain/Scale реализует функцию умножения на K. Установим в поле Gain значение, рассчитанное по формуле (5), (в нашем случае 1,59155).

Управляемый генератор реализован в виде блока FM Function {9} библиотеки Function группы Phase/Freq, в поле Frequency задаётся начальное значение частоты входного сигнала в Герцах (например 80 Гц), в поле Phase - начальная фаза в градусах (например 0), в поле Mod Gain необходимо занести значение 1.

Модели синтезаторов частот

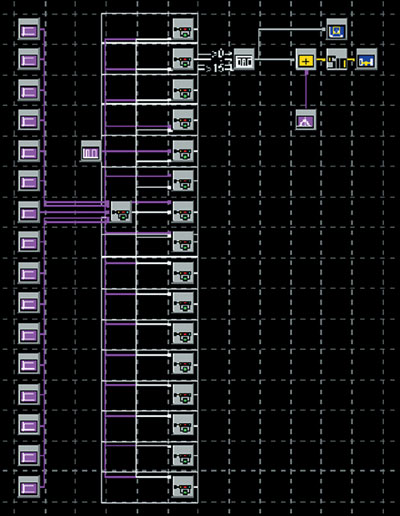

Данный раздел посвящён описанию реализации блоков синтезаторов частот. Блоки выполнены однотипно и построены на принципах прямого синтеза частоты. На рис. 4 приведён внешний вид модели.

Рисунок 4. Модель блока СГС/СТС

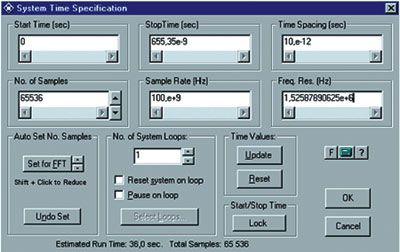

Рисунок 5. Временные параметры модели: Start Time (c) - время начала отсчётов; Stop Time (с) - время останова отсчётов; Time Spacing (с) - временной шаг; No. of Samples - количество отсчётов; Sample Rate (Гц) - частота дискретизации; Freq. Res. (Гц) - частотное разрешение

В дальнейшем будут использоваться порядковые номера, указанные в левом верхнем углу каждого блока модели.

Временные параметры модели указываются в окне System Time Specification, вызываемом кнопкой Define System Time (Ctrl-T). Системная частота дискретизации Sample Rate (Гц) и длительность реализации Start time - Stop time (с) устанавливаются в окне "Define system time" (значок {10} на панели инструментов) (рис. 6).

Рисунок 6. Параметры генератора постоянного напряжения

Блоки 156–163 и 439–446 составляют 16-разрядный регистр кода частоты, блок 156 является младшим разрядом, а 446 - старшим разрядом. Элементы регистра реализованы в виде генераторов постоянного напряжения.

Устанавливая значение амплитуды (Amplitude, V) равным 1 или 0, можно задать состояние регистра. Начальное время (Start time (c)) и сдвиг напряжения (Offset (B)) должны быть равны 0.

Блоки 0, 19, 38, 58, 77, 78, 115, 116, 287–294 образуют 16-разрядный сумматор, параметры данных блоков не должны подвергаться измерению.

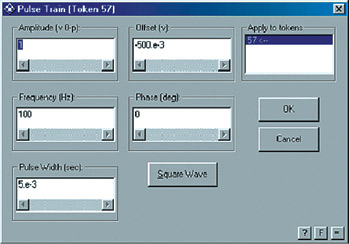

Блок 57 является задающим генератором (рис. 7).

Рисунок 7. Параметры генератора прямоугольных импульсов

Частота следования импульсов определяет частоту на выходе синтезатора. Порядок определения частоты описан в разделе 2. Требуемое значение частоты записывается в окно Frequency (Гц). Поскольку импульсы должны иметь длительность, равную половине периода, то необходимо с помощью кнопки Square Wave установить соответствующую длительность в окне Длительность импульса (Pulse Width (c)).

Блок 153 является матрицей значений фазы одного периода гармонического колебания.

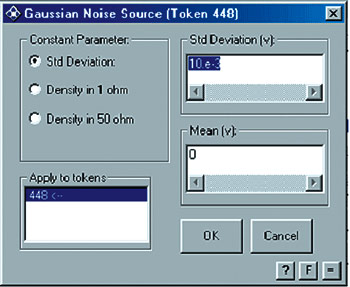

Блок 448 является генератором гауссовского шума (рис. 8).

Рисунок 8. Параметры генератора гауссовского шума

Значение среднеквадратического отклонения (Std. Deviation (B)) определяет спектральную чистоту сигнала синтезатора. Значение СКО 10-3 позволяет удовлетворить требованиям по обеспечению требуемого уровня спектральной плотности мощности фазовых шумов в выходном сигнале:

- минус 70 дБ/Гц при расстройки на 100 Гц;

- минус 80 дБ/Гц при расстройки на 1 кГц;

- минус 85 дБ/Гц при расстройки на 10 кГц.

Изменение данного значения ведёт к изменению данных значений.

Рассмотрим два типичных примера синтезаторов прямого синтеза частот.

Пример 1.

Синтезатор должен формировать сетку частот в диапазоне от 0 до 5 МГц с шагом 10 кГц.

Формула связи между числом, подаваемым на сумматор, размером памяти, частотой опорного сигнала и частотой выходного сигнала:

где k - число, подаваемое на сумматор; С - ёмкость памяти в элементах.

В модели ёмкость памяти равна 216–1, то есть дискрет отрабатываемой сетки частот составляет fon/65535. Взяв, к примеру, опорную частоту 655,35 МГц, можно с дискретом 10 кГц синтезировать частоты от 10 кГц (k = 1 = 0000000000000001b) до 5 МГц, считая k = 500 = 111110100b.

Пример 2.

Синтезатор должен формировать сетку частот в диапазоне от 0 до 400 МГц с шагом 5 МГц.

Формула связи между числом, подаваемым на сумматор, размером памяти, частотой опорного сигнала и частотой выходного сигнала:

где k - число, подаваемое на сумматор; С - ёмкость памяти в элементах.

В модели ёмкость памяти равна 216–1, то есть дискрет отрабатываемой сетки частот составляет fon/65535. Взяв, к примеру, опорную частоту 6553,5 МГц, можно с дискретом 100 кГц синтезировать частоты от 5 МГц (k = 50 = 110010b) до 400 МГц, считая k = 4000 = 111110100000b.

Авторы будут признательны за любые замечания и пожелания, которые следует направлять по адресу: 107005, Москва, 2-я Бауманская ул., д. 5, МГТУ им. Баумана, кафедра СМ5 "Автономные информационные и управляющие системы", Стешенко В.Б.

Литература

- J. Tierney, С.M. Rader, B. Gold. A Digital Frequency Synthesizer // IEEE Trans. Audio Electroacoust. March 1971. Vol. AU-19. p. 48.

- SystemView. Users Guide. SVU – MG 1099. 285 p.

- SystemView. Student Edition. SVU – MSTU 098. 114 p.

|