| |

А. Гольдшер, П. Дик, Ю. Докучаев, В. Кучерский

Микросхема управления диодными нагрузками А 1211

Микросхема А 1211 (ИС) предназначена для преобразования ТТЛ-уровней в противофазные сигналы, необходимые для управления диодными нагрузками.

Основные характеристики:

- напряжение питания, UCC:

- A 1211A - UCC1 = 5 B;

UCC2 = минус 5 B;

- A 1211Б – UCC1 = 9 B;

UCC2 = минус 9 B;

- количество преобразователей - 3;

- номинальный ток нагрузки, IH - 20 мА;

- время установления выходного сигнала, tуст - 50 нс (при номинальных режимных токах потребления);

- допускается асимметричное питание при условиях:

- UCC1

2 В; |UCC2| 2 В; |UCC2|  2 В; 2 В;

- UCC1 + |UCC2|

10 В (18 В) для А 1211А (А 1211Б). 10 В (18 В) для А 1211А (А 1211Б).

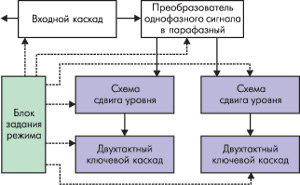

Функциональное назначение микросхемы, требования к её параметрам и режимам эксплуатации предопределили структурную схему ИС. Она приведена на рис. 1.

Рисунок 1. Структурная схема ИС А 1211

В частности, согласование с ТТЛ входными сигналами обусловило необходимость использования одного из известных вариантов стандартных ТТЛ (ТТЛШ) входных каскадов [1]. Дифференциальная нагрузка потребовала наличия в ИС блока преобразования однофазного входного сигнала в парафазные. Парафазные сигналы через согласующие элементы сдвига уровня подаются на выходные каскады, формирующие двухполярный выходной ток в резистивно-диодной нагрузке.

К выходным каскадам предъявляется ряд специфических требований, определивших их структуру. Известные схемотехнические решения их реализации или не обеспечивают симметрию выходных импульсов относительно шин питания [2], или же характеризуются большой потребляемой мощностью и одновременно низким быстродействием из-за ограниченного усиления выходных транзисторов [3].

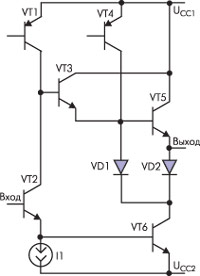

На рис. 2 представлена упрощённая принципиальная схема двухтактного ключевого выходного каскада, предложенная авторами.

Она содержит фазоинвертор с динамической нагрузкой на транзисторе VT2, верхнее плечо на VT3 и VT5, нижнее плечо на VT6 и элементы защиты от сквозных токов на VD1, VD2.

Рисунок 2. Упрощённая принципиальная схема двухтактного ключевого выходного каскада

Установившееся значение выходного напряжения высокого уровня UOH определяется напряжением источника питания UCC1 за вычетом напряжения насыщения коллектор-эмиттер транзистора VT4 и напряжения на прямосмещённом переходе база-эмиттер VT5. Выходное напряжение низкого уровня UOL задаётся напряжением источника UCC2 за вычетом напряжения насыщения коллектор-эмиттер транзистора VT6 и напряжения на прямосмещённом диоде VD2. Следовательно, предложенная схема обеспечивает одно из важнейших требований, предъявляемых к ИС управления диодными нагрузками, - максимальный размах и симметрию выходных сигналов.

Особенность схемы состоит в том, что положительный перепад выходного напряжения формируется в два этапа: а) ускоренное нарастание за счёт каскадного соединения транзисторов VT3 и VT5; б) дополнительное увеличение выходного уровня после выключения VT3 транзистором VT5 и генератором тока на VT4. За счёт этого достигается высокое быстродействие, сопоставимое со схемой на составных транзисторах [2].

Выполнение элементов сдвига уровня на торцевых p-n-p-транзисторах позволило обеспечить "гибкий" выбор напряжений источников питания (без ухудшения динамических параметров ИС). Регулируемый блок задания режима позволяет оптимизировать энергетические и динамические характеристики, в зависимости от конкретного применения ИС в аппаратуре. Это достигается путём подключения внешнего резистора Rрег. В частности, при минимальных средних токах потребления IПОТ.ср.реж., равных 1,5 и 3,0 мА для А 1211А и А 1211Б, соответственно, величины tуст. ~150 нс.

Микросхема содержит три преобразователя уровней на одном кристалле, два из которых объединены по источнику питания UCC1, а один - автономен.

В качестве элементной базы ИС использованы n-p-n высокочастотные транзисторные структуры, преимущественно с диодами Шоттки, и p-n-p торцевые транзисторы, в том числе многоколлекторные [4].

В основу технологического процесса изготовления ИС положена планарно-эпитаксиальная технология с изоляцией элементов обратно-смещённым p-n-переходом. При этом изолирующая диффузия бора осуществляется с использованием сильнолегированных p+-слоёв (Ns ~ 5·1020 ат./см³) и с сохранением боросиликатного стекла, что, по сравнению с обычно применяемыми режимами (Ns ~ 4·1018 ат./см³), позволило уменьшить ёмкость изолирующих p-n-переходов примерно в 1,5 раза за счёт уменьшения составляющей, обусловленной ёмкостью боковых стенок [5].

К технологическим особенностям ИС следует также отнести:

- использование процессов ионного легирования сурьмы, бора и фосфора, обеспечивающих высокую воспроизводимость электрофизических параметров слоёв в широком диапазоне концентраций легирующих примесей;

- малые глубины залегания р-n-переходов, составляющие доли мкм, что при соответствующей геометрии элементов ИС и технологическом процессе их изготовления обеспечило величину граничной частоты усиления по току n-р-n-транзисторных структур fГР порядка 2 ГГц;

- малые размеры элементов, в наибольшей степени влияющих на быстродействие микросхемы. Минимальный размер эмиттера, в свою очередь, ограничен требованиями по величине сопротивления тела коллектора rК транзисторных структур;

- использование двухуровневой металлизации на основе алюминия, легированного кремнием. В качестве межслойного диэлектрика применена плёнка диоксида кремния SiO2, частично легируемая фосфором.

Основные параметры ИС приведены в таблице.

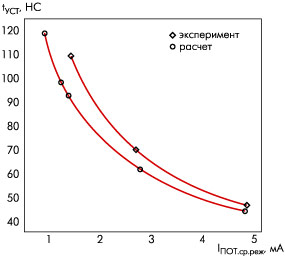

На рис. 3 приведены экспериментальные и расчётные зависимости усреднённого времени установления выходных сигналов tуст от величины среднего режимного тока IПОТ.ср.реж для микросхемы А 1211А.

Рисунок 3. Зависимость времени установления выходного сигнала tуст от величины среднего режимного тока

Параметры моделей для расчётов выбирались с учётом электрофизических и топологических характеристик транзисторных структур. Однако, в используемых моделях не учитывались нелинейность емкостей переходов от напряжения, а также процессы накопления носителей при насыщении транзисторов. Правда, последний эффект, по всей видимости, в меньшей степени сказывался на результатах расчётов, так как в разработанных ИС преимущественно использованы транзисторные структуры с диодами Шоттки. В точке, соответствующей максимальному быстродействию, совпадение экспериментального и расчётного результатов достигалось путём подбора времён пролёта неосновных носителей через базу p-n-p-торцевых транзисторов, tTN, поскольку задержки формирования выходных импульсов в микросхеме в значительной степени определяются передачей сигналов через схемы сдвига уровня, выполненные на их основе. Наиболее близкое к эксперименту значение было получено при tTN ~ 20 нс. При уменьшении режимного тока ИС расчётные характеристики оказываются лучше экспериментальных примерно на 20%.

Конструктивно микросхемы выполнены в корпусе Н06.24-2b с планарным расположением выводов. Возможна поставка ИС и в бескорпусном исполнении (модификация 4).

Таблица. Основные параметры микросхем А 1211

|

Наименование параметра, единица измерения, буквенное обозначение

|

Тип микросхемы

|

|

А 1211А

|

А 1211Б

|

|

не менее

|

типовое

|

не более

|

не менее

|

типовое

|

не более

|

|

Напряжение высокого уровня на прямом и инверсном выходах UOH*, В

|

3,5

|

4,1

|

-

|

7,5

|

8,1

|

-

|

|

Напряжение низкого уровня на прямом и инверсном выходах UOL*, В

|

минус 3,5

|

минус 3,8

|

-

|

минус 7,5

|

минус 8,8

|

-

|

Время установления выходного сигнала tуст., нс, при среднем токе потребления от источников UCC1, UCC2:

1,5 мА для А 1211А; 3,0 мА для А 1211Б

5,0 мА для А 1211А; 10,0 мА для А 1211Б

|

-

-

|

150

50

|

500

60

|

-

-

|

150

50

|

500

60

|

Литература

- Шагурин И.И. Транзисторно-транзисторные схемы. М.: Советское радио, 1974.

- Аналоговые и цифровые интегральные схемы. С.В. Якубовский, Н.А. Барканов, Б.П. Кудряшов и др.; Под ред. С.В. Якубовского. М.: Сов. радио, 1979. с. 59.

- Гребен А.Б. Проектирование аналоговых интегральных схем. Пер. с англ. М.: Энергия, 1976. с. 131.

- Гольдшер А.И. Быстродействующие микросхемы управления приборами с зарядовой связью. Электронная промышленность, 1993. вып. 6-7. С. 57–67.

- Вопросы изоляции элементов микросхем p-n переходом /А.И. Гольдшер, В.И. Диковский, Г.Д. Колмогоров, И.И. Моин/ Электронная техника. сер. 2. Полупроводниковые приборы, 1974. вып. 7. С. 25–34.

|