| |

Т. Келин, Д. Супонников

Построение ИКМ коммутаторов с памятью

Активный рост сектора телекоммуникаций на рынке услуг привел к возникновению острой потребности производителей оборудования связи в специализированных БИС, что диктуется необходимостью снижать стоимость изготавливаемых узлов, не проигрывая при этом в функциональности и спектре решаемых задач.

Статья знакомит читателя с принципами коммутации разговорных и контрольных каналов в современных АТС. Приведен пример построения безблокировочного пространственно-временного коммутатора. Дано краткое описание специализированных БИС этого направления, выпускаемых фирмой Infineon Technologies AG.

Быстрые темпы перевода аппаратурной части АТС на современную технологическую базу ярко отразились и на компонентном составе коммутационных полей (КП), являющихся центральным звеном любой коммутационной или абонентской станции. Так, за последние 20 лет реализация КП размером 8192x8192 канала упростилась настолько, что типовую стойку с несколькими десятками ТЭЗ теперь заменяет одноплатный модуль с четырьмя-пятью БИС.

Начало развития цифровой аппаратуры коммутации можно отнести к первой половине семидесятых, когда на смену автоматическим подстанциям координатной системы стали приходить первые АТС с коммутацией цифровых сигналов во временной области. Спустя десятилетие на рынке появились и цифровые АТС, использующие переключение каналов как во временной, так и в пространственной областях, что существенно повысило гибкость аппаратуры и абонентскую ёмкость.

Типы КП и принципы их функционирования

В эпоху аналоговых АТС, использующих декадно-шаговые и координатные КП, коммутация, очевидно, могла производиться лишь в пределах пространственной координаты, когда входящая абонентская линия непосредственно подключалась на выбираемый исходящий межстанционный канал. Применение частотного разделения каналов (ЧРК) при этом никоим образом не изменяет сути такого определения, так как все каналы используются без соотнесения к временной координате.

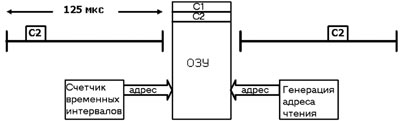

Появление недорогих средств преобразования аналогового сигнала в цифровую форму сделало возможным использовать временную координату для разделения каналов (ВРК). При этом коммутация оказалась возможной во временной области. Принцип такой коммутации основан на перемещении кодовой комбинации, представляющей собой данные канала, из одной временной позиции в другую. При этом виде соединений обязательно возникают задержки между появлением кода на входе и помещением его на выход (рис. 1), так как данные до непосредственного подключения к выходному сдвиговому регистру помещаются в буферную память, которую в дальнейшем будем называть информационной (ИП). Кроме того, имеется два способа управления работой памяти: последовательная запись входящих каналов и произвольное считывание; произвольная запись и последовательное считывание.

Рисунок 1. Принцип коммутации с ВРК

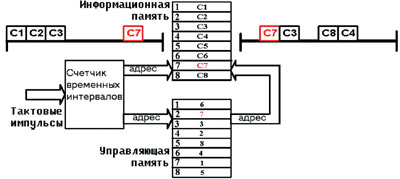

Первый из названных способов отображен на рис. 2: кодовые слова (КС) C1, C2,..., C8, относящиеся к отдельным каналам входного тракта, последовательно помещаются в ячейки ИП. Также последовательно просматривается и управляющая память (УП), назначение которой - поставить в соответствие каждому каналу выходного тракта адрес ячейки ИП. Другими словами, адрес УП есть номер выходного канала, а содержимое ячейки ИП - адрес ИП, по которому находится КС, перемещаемое на выход.

Рисунок 2. Управление памятью методом последовательной записи – произвольного считывания

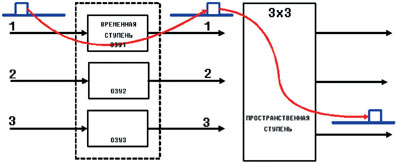

Достоинством временного коммутатора (ВК) является простота управления и отсутствие потерь соединений из-за внутренних блокировок, которые присущи полям с пространственной коммутацией [1]. Недостаток ВК - ограничение коммутационной ёмкости вследствие конечного быстродействия запоминающего устройства. Действительно, скорость работы мультиплексора, осуществляющего переключение во временной области, напрямую зависит от интервала дискретизации аналогового сигнала и числа каналов в кадре тракта ВРК. Чтобы избежать такого ограничения, используют совмещённые, так называемые двухкоординатные КП, в которых за временной ступенью коммутации следует пространственный мультиплексор (рис. 3). В таком варианте построения КП, назначение ступени временной коммутации - обеспечить задержку КС, поступающих в течение временных интервалов, соответствующих входящим каналам, до момента наступления временного интервала, соответствующего нужному исходящему каналу. Как только данный момент наступает, задержанное КС проходит через ступень пространственной коммутации на соответствующий исходящий тракт. На рисунке показано, что КС, поступающее в течение временного интервала 2 по линии 1, задерживается до тех пор, пока не наступит временной интервал 5.

Рисунок 3. Структура двухкоординатного КП

Ступенью пространственной коммутации управляет соответствующая ей УП, которая содержит информацию, необходимую для определения той конфигурации ступени временной коммутации, что должна быть создана в течение каждого временного интервала цикла. Необходимая управляющая информация считывается последовательно, так же, как и из УП временной ступени.

Наибольшей гибкостью обладают структуры с чередованием временных и пространственных ступеней. На входе и выходе такие КП используют временные звенья, а между ними - одно или несколько пространственно-временных звеньев. Такая структура коммутационного поля используется, например, в известной АТС 5ESS производства фирмы AT&T. С другой стороны, в АТС DX-200 использовано полностью временное КП, что позволило избежать блокировок соединений в принципе [2].

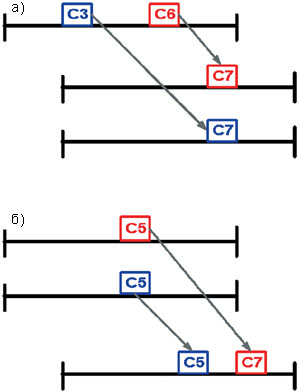

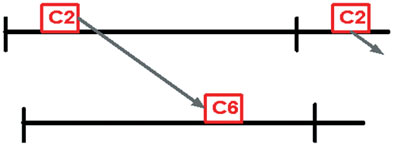

Вероятность возникновения блокировки в двухкоординатных КП обычно невелика и колеблется в диапазоне от 10-3 до 10-20, что зависит от числа попыток установки соединения и внутренней организации структуры поля. На рис. 4 показаны возможные блокировки для вариантов временно-пространственной и пространственно-временной ступеней. В первом случае предпринимается попытка переключения двух разных каналов одного входящего тракта на две одинаковые временные позиции двух исходящих трактов. При этом КС двух входящих каналов должны быть считаны под контролем УП одновременно, что для реализации ИП на обычном ОЗУ невозможно. Во втором варианте два одинаковых канала двух входящих трактов должны быть скоммутированы на одну внутреннюю пространственную линию, что также приведёт к блокировке одного из каналов.

Рисунок 4. Возможные блокировки: а) для временно-пространственной ступени; б) для пространственно-временной ступени

Тем не менее, существует возможность построения безблокировочных двухкоординатных коммутаторов. Одна из таких реализаций КП 4x4x4 (четыре входящих/исходящих тракта с 4 4-бит словами) представлена в конце обзора. В основе этого КП лежит информационная память на сдвиговых регистрах и УП с объединением функций контроля временной и пространственной ступеней. Другим возможным методом уменьшения или полного исключения возможности блокировки является повышение внутренней частоты тактирования схем КП по отношению к символьной скорости в каналах.

Задержки в коммутационных полях

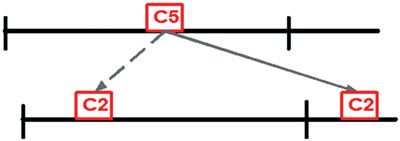

Переключение каналов во временной области неизбежно сопровождается запаздыванием появления данных в выходном тракте. При определённом соотношении временных позиций входного и выходного каналов, такая задержка может быть равной нулю, то есть переключаемое КС может быть передано на выход в пределах того же кадра, в котором оно присутствовало на входе (рис. 5). В ином случае (рис. 6) задержка будет равна одному кадру. А в двухкоординатных КП со сложной внутренней структурой такая задержка может достигнуть значения в три кадра. Такие переключения, задержка передачи данных в которых зависит от указанных факторов, называются соединениями с минимальной задержкой (СМЗ). Этот вид соединений в минимальной степени использует ресурсы коммутационного поля, но не подходит для систем передачи данных, использующих в качестве транспорта более одного канала.

Рисунок 5. Передача КС с нулевой задержкой

Рисунок 6. Передача КС с задержкой на кадр

Другой тип соединений, называемый соединениями с постоянной задержкой (СПЗ), обеспечивает фиксированную задержку данных между входом и выходом с помощью дополнительной "теневой" буферной памяти во временном звене коммутатора. При этом текущая ИП состоит из двух частей, одна из которых доступна для чтения в течение кадра, а другая - для записи входящих каналов. По окончании текущего кадра "половинки" меняются местами. СПЗ могут использоваться не только для коммутации многоканальных трактов передачи данных, но и для голосовых каналов.

В приводимом ниже описании мультиплексора на языке Verilog реализуется возможность установления только СПЗ с величиной запаздывания в один кадр.

БИС коммутационных полей

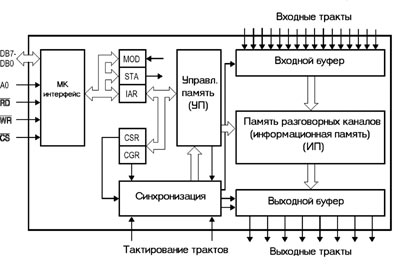

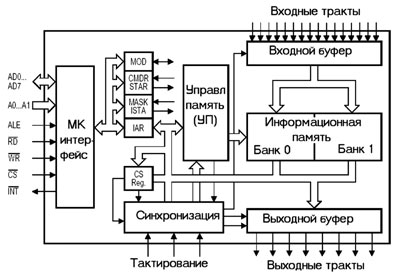

В настоящее время уровень интеграции БИС позволил провести глубокую унификацию производства коммуникационного оборудования. В свою очередь, это коснулось и принципов построения КП современных АТС. Возможность объединения на одном кристалле сверхбыстродействующего ОЗУ и распределённых схем управления позволила производителям электронных компонентов начать выпуск безблокировочных двухкоординатных коммутаторов, реализующих более двух тысяч одновременных соединений. Одним из лидеров в разработке и выпуске таких БИС оказалось отделение полупроводников фирмы SIEMENS, позже вылившееся в группу Infineon Technologies AG. Первые интегральные микросхемы серии MTSC (Memory Time Switch CMOS) для построения КП были выпущены в начале 90-х годов. Серия MTSC состояла из 6 микросхем с различной коммутационной ёмкостью и типом соединений. Так, ресурсами чипа PEB2047 можно было устанавливать до тысячи соединений с постоянной или минимальной задержками (рис. 7). Более простое устройство PEB2045 не позволяло устанавливать СПЗ, поэтому на функциональной схеме этого устройства информационная память обозначалась как "голосовая память", чем подчёркивалась возможность коммутации лишь СМЗ (рис. 8).

Рисунок 7. Структура БИС PEB2047

Рисунок 8. Структура БИС 2045

В 2000 году фирма Infineon представила миру новое семейство коммутационных БИС SWITI, состоящее из 6 чипов, разделенных на две группы - MTSI и HTSI. Вторая группа, имея полное сходство основной части с первой, позволяет пользователю для расширения системы использовать шинный интерфейс H.100/H.110. При сохранении коммутационной ёмкости, свойственной предыдущему семейству, SWITI обеспечивает широкий выбор возможностей управления типами соединений и режимов работы ИКМ интерфейса. Любое соединение может быть объявлено, как одно-, 2-, 4- или 8-битное. Кроме этого, управляющая программа может произвольно задавать тип задержки (минимальная или постоянная) соединения, а наличие гибкой контролируемой петли ФАПЧ в составе устройства даёт возможность использовать микросхемы семейства в составе самого различного, не обязательно относящегося к АТС, оборудования.

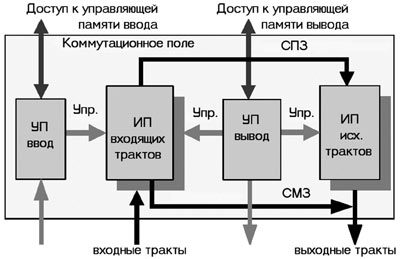

Одним из принципиальных отличий в построении КП БИС семейства SWITI стал принцип перемещения данных с входных линий на выходные. "Традиционный" метод подразумевал последовательную запись входящих каналов в ИП, содержимое которой просматривалось, соответственно, указателю в УП. Этот способ рассмотрен выше. Чтобы обеспечить большую гибкость в управлении соединениями, фирма Infineon построила схему, в которой запись входящих кодовых слов контролирует УП номер 1, а передачей на выход - второй блок УП (рис. 9). Существенным недостатком такой реализации можно определить значительно большую схемную сложность, и большее время для первоначальной установки соединения, что вытекает из необходимости поддерживать протокол "рукопожатия" с УП, доступ к которой нельзя осуществить одновременно как со стороны внутреннего автомата, так и со стороны управляющего интерфейса.

Рисунок 9. Структура БИС КП семейства SWITI

Описание ИКМ коммутатора на языке Verilog

Моделирование и создание логической структуры современных БИС уже давно немыслимо без применения специализированных САПР и языков описания аппаратуры. Заинтересованному читателю предлагается самостоятельно ознакомиться с одним из возможных вариантов реализации безблокировочного двухкоординатного коммутатора. Описание на языке Verilog, файлы управления проектом в среде синтезатора Leonardo Spectrum и результаты работы симулятора САПР Max+Plus II доступны в сети общего пользования Интернет по адресу: http:// www.evm90.com/tkds/PCM_switcher.zip.

Для сокращения времени компиляции и качественной оценки работоспособности размеры кодовых слов в каналах, равно как и их число и число трактов, уменьшено до четырёх. Входными сигналами для модуля являются: тактирование и кадровый синхроимпульс ИКМ-интерфейса, входящие ИКМ-тракты, тактирование двухпортовой управляющей памяти (УП), строб записи в УП, комплексные (линия + канал) адреса входного и выходного каналов. Выходами схемы являются 4 линии ИКМ.

В качестве УП использован модуль двухпортовой памяти, полученный с помощью программы genmem.exe, входящей в состав пакета Max+Plus II. Блоки ИП построены на регистрах сдвига, что значительно упрощает описание коммутатора, не умаляя наглядности его функционирования. Отказ от реализации ИП на сдвиговом регистре и применение обычного ОЗУ повлёк бы синтез мультиплексора с наличием блокировок или же усложнение схем управления памятью и повышение тактовой частоты. В приводимом же модуле за основу взята максимальная простота описания для получения качественных оценок.

Литература

- Гольдштейн Б.С. Сигнализация в сетях связи. М.: Радио и связь, 1998. Т. 1. С. 7–32.

- Штагер В.В. Цифровые системы связи. Теория, расчет и оптимизация. М.: Радио и связь, 1993. С. 116–155.

- Ситняковский И.В., Мейкшан В.И., Маглицкий Б.Н. Цифровая сельская связь. М.: Радио и связь, 1994. С. 163–181.

- HTSI_DS.book - Infineon Technologies AG - 2001. P. 3–24.

- MTSXMTSI.book - Infineon Technologies AG - 2001. P. 1–11.

|