| |

С. Волков, А. Ефишин, С. Морозов, С. Соколов

Проблема электростатического разряда и современные методы защиты интегральных схем от него. Часть 1

Статья открывает цикл публикаций, посвященных проблемам статического электричества в микроэлектронике и методам предотвращения или ослабления его влияния на параметры и характеристики интегральных схем (ИС).

В отличие от предшествующих публикаций, в статьях цикла будут рассмотрены, главным образом, технологические и топологические методы, конструктивные элементы и средства для борьбы с электростатическими разрядами непосредственно на кристалле ИС.

ESD и варианты его возникновения в ИС

Электростатический разряд (ElectroStatic Discharge, ESD) представляет собой существенную опасность для ИС, и разработка защитных элементов от него - важная ступень проектирования устройства. Тенденции развития полупроводниковой промышленности непосредственно связаны с уменьшением минимальных топологических размеров проектирования ИС, что приводит к большей чувствительности устройств по отношению к внешним факторам и, в частности, к ESD. Природа ESD может быть различной, поэтому невозможно обеспечить защиту компонентов во всех возможных ситуациях. Для стандартных сценариев были разработаны следующие тестовые схемы для определения чувствительности ИС к ESD [1,2].

Модель человеческого тела (Human Body Model, HBM)

В результате контакта человеческого тела с устройством может произойти ESD. Тело может обладать отличным от земли потенциалом, например, в результате трения. Тестовая схема для этого случая представлена на рис. 1a.

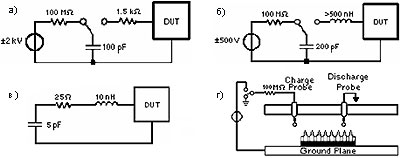

Рисунок 1. Тестовая схема модели: а) человеческого тела; б) механической модели; в) модели заряженного устройства; г) устройства для CDM

В этой схеме конденсатор (С = 100 пФ) заряжается через высокоомный резистор (R = 100 МОм) напряжением ±2 кВ, затем разряжается через 1,5-кОм резистор в тестируемое устройство. Конденсатор моделирует ёмкость человеческого тела, которая на самом деле может варьироваться до 500 пФ. Сопротивление человеческого тела также может изменяться в достаточно широких пределах - от нескольких десятков Ом до сотен кОм, в зависимости от условий. Напряжение разряда также может достигать 4 кВ. Согласно существующим стандартам, имеется ряд тестовых схем для различных устройств. Данная схема соответствует тестированию ИС. Одним из самых важных параметров в тесте является время нарастания тока во время разряда. Оно должно быть порядка десятых долей наносекунд. Но при этом важно заметить, что ток разряда не сразу распространяется по проводящей области. Поэтому в начале существует опасность перегрузки защитной схемы. С другой стороны, этот вариант может быть не так опасен, так как ESD происходит, как правило, не в самой схеме, а где-то на корпусе или на связанном с контактом проводнике, который, в свою очередь, обладает достаточно высокой индуктивностью, дающей защитной схеме время полностью включиться.

Механическая модель (Machine Model, MM)

ESD в данной модели возникает в результате различных механических воздействий, всегда имеющих место в оборудовании для производства ИС. Корпус и механизмы такого оборудования сделаны из металла, но неизбежно содержат различные пластиковые части (например, подшипники), сильно отличающиеся по размерам и формам. При движении этих частей может создаваться электростатический заряд и происходить его разряд. На рис. 1б изображена тестовая схема для этой модели.

Эта тестовая схема аналогична предыдущей, с той лишь разницей, что сопротивление металлических частей устройства мало, что приводит к значительно большему пиковому току в тестируемом устройстве. Но зато в результате большой индуктивности, имеющей место в данном случае, перегрузки защитной схемы не происходит, амплитуда и время роста тока ограничены. Энергия, имеющая место в этой модели, выше, чем энергия HBM вследствие отсутствия сопротивления. Поэтому важно заметить, что для того, чтобы не допустить повреждения тестируемого устройства, необходимо снизить напряжение до ±200 В.

Модель заряженного устройства (Charged-Device Model, CDM)

Ещё один вариант возникновения ESD, который необходимо учитывать, может происходить во время работы ИС. Нельзя точно для этого случая воспроизвести профиль неправильной работы ИС при ESD с помощью тестового оборудования. При возникновении электростатического разряда в самом устройстве пиковый ток ESD больше, чем в любом из рассмотренных случаев, и поступает в тестируемое устройство почти без задержки (время роста меньше 200 пс), что делает разработку защитных схем для этой модели наиболее сложной. Тестовая схема этой модели представлена на рис. 1в.

Также необходимо заметить, что между моделями человеческого тела и заряженного устройства отсутствует корреляция, то есть компоненты, сохраняющие работоспособность в первом случае, не обязательно будут работать в тесте CDM.

Один из вариантов тестирования устройства представлен на рис. 1г.

Тестируемое устройство размещено обратной стороной на металлической пластине, чем обеспечивается максимально возможная ёмкость разряда. Устройство заряжается первым подвижным тестером и разряжается вторым.

Модель заряженного кабеля (Charged-Cable Model, CCM)

Типичной проблемой, связанной с использованием электрического оборудования, является соединение контактов с кабелем. Емкость десятиметрового кабеля порядка 100 пФ может вызвать электростатический разряд напряжением до 1 кВ. При этом рассеивается около 500 мкВт энергии, что во много раз больше, чем в предыдущих тестах. Разрядный ток, протекающий через импеданс кабеля, порядка 10 А. Однако вследствие высоких индуктивностей гнезда и присоединяемого кабеля не происходит мгновенного роста тока.

Все представленные модели являются лишь аппроксимацией реальности. На самом деле паразитные конденсаторы и индуктивности могут значительно уменьшать точность воспроизведения модели. Влияние паразитов наиболее велико для модели заряженного устройства. Несмотря на всё это, опираясь на эти модели, можно обеспечить хорошо воспроизводимые результаты для ИС, подверженных ESD.

Модель импульса линии передач

Защищённость устройства от электростатического разряда по одной из вышеописанных моделей не гарантирует полной защищённости от ESD. Более того, возможна такая ситуация, когда схема будет работать при высоком уровне ESD и будет повреждаться при более низком. Существует ряд ограничений при использовании моделей для исследования выносливости ИС к ESD. Использование этих моделей даёт неполный взгляд на то, как ведёт себя защищаемое устройство под воздействием ESD. Форма входного сигнала HBM и других моделей достаточно сложна, соответственно сложной является форма выходного импульса. Вследствие этого, классические модели используются как некий "чёрный ящик". Важно лишь, выдерживает разработанное устройство данный стрессовый уровень или нет.

Использование модели импульса линии передач (Transmission Line Pulsing, TLP) даёт возможность получить ряд важных характеристик без повреждения устройства. Тестовая схема для данного метода показана на рис. 2 [9].

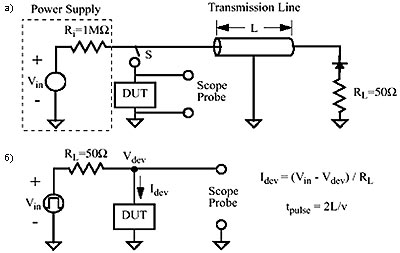

Рисунок 2. Кабель длины L заряжается до напряжения Vin и затем разряжается через переключатель S (а); эквивалентная схема модели (б)

Коаксиальный кабель заряжается до определённого напряжения и затем разряжается на входную/выходную контактную площадку устройства.

Данный метод имеет много общего с HBM, так как здесь имеет место разряд конденсатора в тестируемое устройство. Но с другой стороны, ёмкость для TLP является распределённой, обеспечивая тем самым прямоугольный входной импульс длиной 100 нс и со временем роста около 2 нс. Высота импульса составляет приложенное напряжение Vin, ширина импульса 2L/v, где L - длина кабеля и v - скорость изменения фазы. Если импеданс устройства является величиной постоянной, то линия передачи будет представлять постоянный по току импульс. С помощью осциллографа можно измерить падение напряжения на устройстве. Ток также может быть измерен или вычислен при известных входном напряжении и падении напряжения на устройстве:

Idev = (Vin – Vdev)/Rl.

Для предотвращения многократных отражений, когда импеданс устройства меньше 50 Ом, с другой стороны линии передачи по отношению к тестируемому устройству включается диод и резистор.

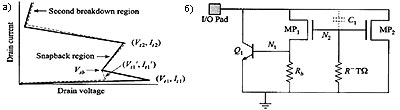

Одним из основных преимуществ применения TLP является получение ВАХ защитных элементов. Посылая на вход устройства последовательность увеличивающихся импульсов и выводя на экран соответствующую последовательность выходных напряжений и токов, можно получить данную ВАХ. Чтобы не допустить разрушения устройства вследсствие перегрева, необходимо обеспечить достаточный промежуток времени между двумя стрессами: ~ 1–2 с. Из этой ВАХ можно получить такие параметры, как напряжение включения защитного устройства, напряжение включения режима snapback (рис. 7a), напряжение второго необратимого пробоя. Хотя прямоугольный входной сигнал не даёт точную модель ESD-стресса, результаты такого исследования коррелируют с реальными ESD-стрессами и тестовыми моделями.

Повреждение ИС ESD. Методы разработки защитных цепей

ESD в первую очередь повреждает наиболее слабо защищенные компоненты, что приводит к следующим повреждениям:

- тепловой пробой p-n-перехода;

- возникновение в окисле пустот, нитевидных образований, испарение окисла, что приводит к замыканиям и неправильной работе ИС;

- металлическая разводка и контакты могут плавиться и испаряться, в результате происходят замыкания и отказ ИС.

Тенденции к снижению глубин залегания переходов, уменьшению толщины подзатворного окисла и толщины разводки увеличивают вероятность повреждения устройства электростатическим разрядом. В первую очередь повреждаться будет тонкий подзатворный окисел входных и выходных КМОП-структур и связанная с ними металлическая разводка. Если в качестве контактов используются силициды металлов, это также ухудшает защищённость схемы от ESD. В этом случае имеются специальные схемотехнические и технологические решения, в частности, блокировка силицида, что усложняет технологический процесс и увеличивает стоимость изготовления. Пример применения специальной маски для блокировки силицида показан на рис. 3a [8].

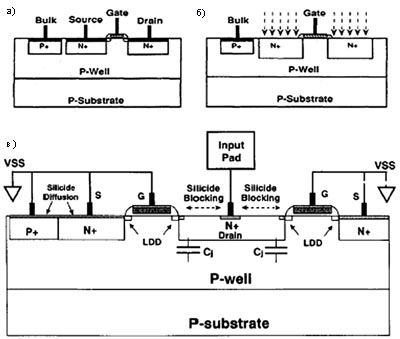

Рисунок 3. Структура n-МОП транзистора с заземленным затвором: а) с применением блокировки силицида в стоковой области; б) c применением технологии LDD; в) блокировка LDD для транзистора из схемы защиты от ESD

На этом рисунке изображена структура транзистора с заземлённым затвором. Блокировка силицида осуществляется в области стока транзистора для обеспечения равномерности протекания тока стока в случае ESD. Подобные проблемы возникают в субмикронной КМОП-технологии, где применяется слабое подлегирование областей стока и истока (Lightly-Doped Drain, LDD) для недопущения смыкания канала. В этом случае также необходимо блокировать силицид в областях стока и истока транзистора в схеме защиты от ESD, как это показано на рис. 3б [7].

Известен целый ряд отдельных устройств защиты от ESD, обладающих хорошими характеристиками, но для наилучшей защиты ИС они должны быть подобраны и включены оптимальным образом, что нельзя сделать автоматически [1]. Существуют два метода разработки суммарной защиты устройства: метод случайного пути и метод выборочного пути.

В методе случайного пути ток ESD находит собственный случайный путь от одной контактной площадки к другой. Слабое звено защитной схемы в первую очередь достигает напряжения пробоя. Эти элементы в разных ситуациях различны. За несколько итераций такие звенья отбираются и отбраковываются. Наконец, достигаются желаемые характеристики по ESD. Метод случайного пути не является универсальным и специфичен не только для технологии, но и для варианта исполнения схемы на кристалле.

Другой метод заключается в направлении тока ESD по определённому пути. Выбранный путь имеет самое низкое сопротивление по сравнению с другими паразитными цепями. В этом методе отладка защитной схемы не занимает так много времени, поскольку поиск и устранение наиболее слабых элементов проще. Метод выборочного пути более подвержен систематизации.

Важно заметить, что устройства, используемые в защитных схемах, можно разделить на два типа: пробойные (Breakdown Devices, BD) и беспробойные (Non-Breakdown Devices, NBD) [1]. Устройства первого типа работают в режиме между первым и вторым (тепловым) пробоем, их действие сильно зависит от топологического исполнения и технологических процессов, вследствие чего их проектирование достаточно сложно. Намного легче использовать беспробойные устройства, то есть работающие в нормальном режиме. Моделирование таких схем легче и её результаты более предсказуемы.

Также важно отметить, что при тенденции к росту числа элементов и, соответственно, размера ИС, происходит увеличение собственной ёмкости устройства. Для поддержания точных значений напряжений питания необходимо использование в ИС развязывающих конденсаторов. Эти конденсаторы в условиях уменьшения величины напряжения питания и роста тока могут оказать значительную помощь в уменьшении напряжения ESD для цепи Vcc-Vss, тем самым защищая основное устройство. Также уменьшение топологических размеров влечёт за собой увеличение рабочей частоты устройства. Это приводит к тому, что время роста ESD импульса для модели заряженного устройства сравнимо со временем работы защитных схем, что позволяет быстрее реагировать на этот импульс.

Режимы тестирования ESD в зависимости от вариантов его возникновения на контактных площадках

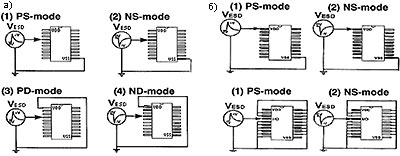

Наиболее часто ESD возникает между контактной площадкой входного сигнала и контактной площадкой одной из шин питания. ESD может иметь положительную или отрицательную полярность по отношению к потенциалам шин питания Vdd и Vss. Таким образом, имеют место четыре режима возникновения ESD на контактной площадке входного/выходного сигнала, приводящие к различным путям протекания стрессового тока. Варианты измерений ESD для этих режимов представлены на рис. 4a [6].

Рисунок 4. Измерение выносливости устройства к ESD для четырёх режимов возникновения разряда между контактной площадкой входного/выходного сигнала и контактной площадкой одной из шин питания (а); дополнительные режимы возникновения ESD на контактной площадке (б)

Для первого режима (PS-mode) положительный по отношению к потенциалу земли (Vss) электростатический разряд подаётся на одну из контактных площадок входных сигналов, шина питания (Vdd) не подсоединена и стрессовый ток покидает устройство через шину земли. Второй режим (NS-mode) - отрицательный относительно потенциала земли ESD стресс на контактной площадке, шина питания не подсоединена, стрессовый ток покидает устройство через шину земли. Для третьего режима (PD-mode) оборвана шина земли, ESD стресс положителен относительно потенциала шины питания, через которую стрессовый ток покидает устройство. Для четвёртого режима (ND-mode) оборвана шина земли, ESD стресс отрицателен относительно потенциала шины питания, через которую стрессовый ток покидает устройство. Во всех 4-х случаях остальные контактные площадки входов/выходов не подсоединены.

Эти стрессовые напряжения могут нанести повреждения как n-МОП, так и p-МОП устройствам входного или выходного буфера. Например, в случае отсутствия защитной схемы от ESD между контактной площадкой и шиной питания будет происходить повреждение ИС. В ND-режиме стрессовый ток сначала потечет через схему защиты от контактной площадки к шине земли, а затем через защитную схему между шинами питания (если таковая имеется) или через элементы внутренней схемы к шине питания Vdd. Также любая КМОП ИС обладает паразитными емкостями и сопротивлениями шин, на которых возникает падение напряжения. Это ведёт к повреждению внутренних элементов ИС, несмотря на имеющуюся защиту. ND-режим ESD приводит к возникновению стрессового напряжения между шинами питания. Если ток ESD не выводится быстро и эффективно из ИС, то могут иметь место повреждения в защитной схеме между Vss и Vdd, а именно разрушения полевого окисла паразитных структур между двумя n+ диффузиями [6].

Таким образом, необходимо обеспечивать защиту от ESD между контактной площадкой и обеими шинами питания, чтобы полностью обезопасить устройство от повреждения в случае возникновения ESD в любом из четырёх режимов.

Но, даже обеспечив полную защиту от вышеперечисленных четырёх режимов возникновения ESD, нельзя быть полностью уверенным в полной защите ИС. Есть вероятность возникновения ESD между контактными площадками входного и выходного сигналов или контактными площадками шин питания. Ток проходит от одной контактной площадки к другой по некоторому пути через внутренние элементы устройства. Для определения защищённости устройства вводятся дополнительные режимы проведения измерений, представленные на рис. 4б.

Для таких условий измерения ESD защиты внутренние элементы достаточно уязвимы даже при наличии полной входной защиты.

В каждом режиме стрессовый ток течёт по своему собственному пути. Также будет происходить повреждение внутренних компонентов при отсутствии какой-либо защиты от ESD кроме входной защиты. Для последних четырёх режимов трудно обнаружить повреждение ИС просто отслеживанием тока утечки. Для этого часто требуется полный функциональный контроль для обнаружения неисправной работы. Для обеспечения хорошей защиты от ESD необходимо тестировать ИС по всем восьми режимам для трёх моделей: HBM, MM, CDM. В случае недостаточной защищённости можно использовать дополнительные защитные элементы между контактными площадками "чистого" и "грязного" напряжения питания, между контактными площадками шин питания, а также улучшать характеристики входной защиты.

Основные элементы защиты от ESD

Основными элементами защиты от ESD являются следующие [1]:

- n-МОП транзистор с толстым подзатворным окислом (Thick Field Oxide, TFO);

- n-МОП транзистор с заземлённым затвором (Grounded Gate NMOS Transistor, GGNMOST);

- кремниевый управляемый диод (Silicon-Controlled Rectifier, SCR);

- устройство, основанное на эффекте смыкания областей пространственного заряда (Punchthrough-Induced Protection Element, PIPE);

- диод Зенера (Zener diode).

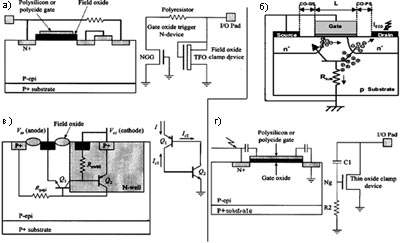

Пример применения TFO показан на рис. 5a.

Рисунок 5. Упрощенная схема применения TFO и структура её выполнения (а); структура GGNMOST (б); структура и схема GCNMOS (в)

Затвор n-МОП транзистора с толстым подзатворным окислом объединён со стоком, но оказывает малое влияние на его ток. Работа устройства происходит следующим образом: большое напряжение ESD, приложенного к контактной площадке, приводит к генерации дырочного тока в области обратносмещённого перехода стока n-МОП транзистора, который течёт в подложку. Этот ток повышает локальный потенциал подложки за счёт её сопротивления. При определённом напряжении Vt1, поданном на вход, начинает работать паразитный латеральный биполярный n-p-n-транзистор (рис. 5a,б).

Это напряжение первого пробоя (рис. 7a).

При этом напряжении переход подложка–исток становится положительно смещенным. Это критерий включения n-p-n-транзистора [1,4].

Участок вольтамперной характеристики (ВАХ) с отрицательным дифференциальным сопротивлением неустойчив, устройство защелкивается и сразу же начинает работать в низкоомной области (snapback region). После вступления в низкоомную область ВАХ транзистор начинает проводить большую часть тока стока, не допуская его в защищаемое устройство. В рассматриваемом случае GGNMOST играет роль управляющего устройства, так как не может провести очень большой стрессовый ток. Он нужен для того, чтобы повысить локальный потенциал подложки и инициировать аналогичный пробой n-МОП TFO, который после включения будет проводить большую часть стрессового тока. Поскольку GGNMOST не может проводить большой ток, необходимо включить в схему резистор, который бы его ограничивал. Заземлённый затвор обеспечивает работу устройства только при электростатическом разряде, при нормальных условиях элемент выключен.

Vt2 и It2 - это напряжение и ток второго, необратимого пробоя, после которого наступает разрушение устройства. Значение It2 зависит от коэффициента b латерального n-p-n-транзистора, длины канала МОП-транзистора, глубины залегания p-n-перехода, толщины эпитаксиального слоя. Чем больше это значение, тем лучше. Обычно оно порядка 10–20 мА/мкм. В низкоомной области величина тока пропорциональна ширине канала транзистора, что связано с положительным температурным коэффициентом. В этом случае ток распределяется равномерно. Но после наступления теплового пробоя температурный коэффициент сопротивления отрицателен, ток концентрируется в определённых местах, его распределение неравномерно. Поэтому независимо от размеров транзистора величина It2 остаётся прежней и может даже уменьшаться с ростом ширины канала. Проанализировав это, можно прийти к выводу, что для обеспечения равномерного протекания тока высокой плотности напряжение Vt2 должно быть больше напряжения первого пробоя Vt1, чтобы после первого пробоя устройство работало в snapback-области, а не в области теплового пробоя (рис. 7a). Этого можно добиться несколькими способами [1]:

- увеличить напряжение затвор–исток Vgs во время электростатического разряда, что приводит к снижению Vt1. Нельзя увеличивать Vgs слишком сильно, это может привести к ухудшению пробойных характеристик;

- уменьшить длину канала, что приведёт к увеличению ß и к снижению Vt1;

- немного увеличить напряжение на подложке, чтобы снизить Vt1;

- добавить в схему резистор.

Таким образом, работа устройства в низкоомной области характеризуется низким напряжением и низким сопротивлением, благодаря этому рассеивание энергии невелико. На этом эффекте основано действие не только TFO, но и некоторых других устройств.

Важным недостатком схемы с устройством TFO является её плохая применимость к силицидным технологиям. Использование силицидных контактов приводит к неравномерному распределению токов в устройстве во время работы. Для предотвращения этого недостатка необходимо блокировать силицид, что делает необходимым дополнительные технологические операции, увеличивающие стоимость изготовления, усложняющие разработку и уменьшающие эффективность.

GGNMOST представляет собой обычный n-МОП транзистор с тонким подзатворным окислом. Исток и затвор подключены к земле. Принцип действия такого элемента был объяснён в предыдущем случае, главное отличие от элемента TFO заключается только в толщине подзатворного диэлектрика. Можно лишь ещё раз подчеркнуть, что для правильной работы устройства и для обеспечения пропорциональности тока по ширине транзистора необходимо обеспечить Vt2 > Vt1. Существуют определенные схемотехнические решения для достижения этих целей [4]. Структура GGNMOST представлена на рис. 5б.

В предыдущем случае рассматривались способы обеспечения правильной работы устройства после первого пробоя. Ещё один вариант обеспечения равномерности протекания тока после первого пробоя - это использование n-МОП транзистора с затвором, связанным с защищаемой контактной площадкой (Gate-Coupled NMOS, GCNMOS) [1]. Структура и схема этого элемента показаны на рис. 5в.

В этой структуре затвор связан с контактной площадкой через конденсатор C1, фактически являющийся фильтром высоких частот вместе с резистором R2. Эта умышленно введенная ёмкость дополняет уже существующую паразитную ёмкость затвор–сток. В первые мгновения ESD этой ёмкости достаточно, чтобы с помощью резистора немного повысить напряжение на затворе. Критерием выбора номиналов конденсатора и резистора является снижение напряжения Vt1 < Vt2. Большим преимуществом данного устройства является его применимость к силицидным технологиям.

Кремниевый управляемый диод (Silicon-Controlled Rectifier, SCR) является одним из самых эффективных средств ESD-защиты. В силу комплементарной природы КМОП-устройств, когда необходимо использование кармана, в них всегда присутствует вышеназванный паразитный элемент. SCR можно эффективно использовать в качестве полной защиты входной/выходной контактной площадки [5]. На рис. 5г представлена схема и структура управляемого диода [1,3].

База p-n-p-транзистора (n-карман) является также коллектором n-p-n-транзистора, а база n-p-n-транзистора в тоже время является коллектором p-n-p-транзистора. Работа устройства основана на эффекте защёлки.

Это так называемый тиристорный эффект, которого стараются избегать в КМОП-структурах, но в данном случае он полезен.

При нормальных условиях работы на n-карман подаётся питание, а на подложку - земля. Если это соотношение нарушается в результате электростатического разряда и потенциал n-кармана становится ниже потенциала подложки, то переход n-карман – p-подложка становится прямо смещённым, и стрессовый ток утекает в подложку. Тиристорный эффект в данном случае отсутствует. Однако более интересен случай увеличения напряжения на кармане, приводящий к пробою обратно смещённого перехода. Ток, протекающий через сопротивления кармана и подложки Rnwell и Rpepi, становится существенным, что приводит к прямому смещению переходов база–эмиттер обоих биполярных транзисторов. Срабатывает тиристорный эффект, и весь стрессовый ток отводится на анод, то есть в данном случае, на контакт земли.

Большим недостатком такой схемы является высокое напряжение защёлкивания устройства, порядка 30–60 В. К тому же время защёлкивания этого устройства около 1 нс, что делает его слишком медленным. Поэтому в чистом виде эта схема практически не используется. Созданы специальные схемы с низким напряжением защёлкивания и управляющими элементами для ликвидации этих недостатков.

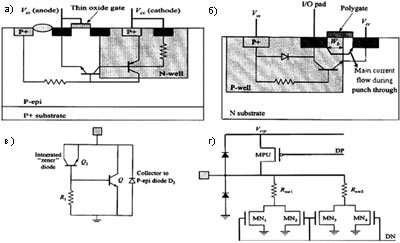

В качестве усовершенствованной схемы SCR [1] можно рассмотреть следующий вариант, представленный на рис. 6a.

Рисунок 6. SCR с низким напряжением защелкивания (LVTSCR) (а); структура PIPE элемента (б); один из вариантов использования диодов Зенера (в); защита выходного буфера с помощью диодов и резисторов (г)

Отличие структуры этого устройства от обычного SCR заключается в использовании общей n+-области между n-карманом и p-подложкой, а также введением в схему МОП-транзистора. Снижение напряжения защёлкивания происходит вследствие того, что пробой перехода n+–pepi происходит при более низком напряжении. Расстояние между общим n+ и n+-анодом должно быть как можно меньше, а уровень легирования этих областей должен быть максимальным. Это обеспечивает более высокий коэффициент a у n-p-n-транзистора. Уменьшение расстояния достигается использованием МОП-структуры, благодаря чему оно становится равным длине канала. Сформированный транзистор представляет собой GGNMOST. Использование этого транзистора позволяет дополнительно повышать потенциал подложки во ESD, тем самым повышая скорость работы устройства [1]. Это устройство обладает высокой скоростью срабатывания при ESD и защёлкивается при 8 В для технологии 0,35 мкм. Но даже такого напряжения недостаточно для защиты n-МОП транзистора в выходном буфере. Этот n-МОП транзистор достигнет первого пробоя в случае ESD раньше, чем защёлкнется SCR. Чтобы этого избежать, можно сделать длину канала GGNMOST в SCR меньше, чем длина канала выходного транзистора, но в обоих случаях этот параметр должен быть как можно меньше и ограничивается лишь возможностями технологии, так что увеличение длины выходного транзистора не самый лучший способ.

Элемент защиты PIPE, основанный на эффекте смыкания областей пространственного заряда, представляет собой ещё одно устройство защиты от электростатического разряда. Его структура показана на рис. 6б [1].

Защищаемая контактная площадка соединена с коллектором латерального n-p-n-транзистора, активной базой которого является часть подложки, ограниченная коллектором.

Переход n+–p-карман обратно смещён при напряжении на входе, большем напряжения земли. Если напряжение на входе превысит напряжение питания Vcc, то область пространственного заряда (ОПЗ) перехода n+–p-карман соединится с ОПЗ перехода p-карман – n-подложка. В этот момент возникает низкоомный путь для тока между входом и Vcc. Протекающий ток помогает открыть n-p-n-транзистор. В этом случае наблюдается резкое снижение напряжения, подобное снижению напряжения в GGNMOST при вхождении в snapback-режим. Изменяя длину затвора, можно моделировать напряжение, при котором происходит слияние ОПЗ. Кроме этого параметра, на это напряжение влияет также степень легирования p-кармана, n+-области и области канала.

Главное преимущество этого устройства заключается в малых размерах и приемлемом быстродействии при ESD. Плохие пробойные характеристики, короткоканальные эффекты, степень легирования кармана влияют на быстродействие устройства. Поэтому трудно воспроизвести устройства с одинаковым напряжением смыкания.

И последнее устройство пробойного типа, которое будет рассмотрено, это диод Зенера. Отличие диода Зенера от обычного заключается в более низком напряжении лавинного пробоя. Диод представляет собой диодное включение транзистора с очень сильно легированными областями. В обычной технологии создание таких диодов затруднено. Один из вариантов применения зенеровских диодов показан на рис. 6в [1].

При ESD происходит пробой диода Зенера. После того как достигается напряжение пробоя, ток течёт через сопротивление в подложку. Это напряжение пробоя, как правило, чуть ниже или равно напряжению Vsb (snapback mode) для n-МОП. Диод Зенера помогает открыться n-p-n-транзистору, который затем проводит большую часть стрессового тока. В другом случае, когда за счёт напряжения ESD потенциал на входе ниже потенциала подложки, большую часть стрессового тока будет проводить диод D2. Такую схему удобно использовать в БиКМОП-технологии, так как в ней присутствует биполярный транзистор, использование которых в КМОП-технологии затруднено.

В качестве беспробойных защитных устройств используются обычные диоды, МОП и биполярные транзисторы. Вариант защиты выходного буфера с помощью диодов показан на рис. 6г [1,2].

Как видно на рис. 6г, диоды включаются и проводят ток только в случае ESD. Это традиционный способ защиты схем, он очень удобен, поскольку экономит площадь, к тому же с учётом тенденции к уменьшению размеров кармана, n+ и p+-областей, роста уровня легирования кармана, диодная защита становится всё более быстродействующей и низкоомной. Но у неё есть свои недостатки. Диоды в КМОП-технологии представляют собой включенные соответствующим образом биполярные транзисторы, что при последовательном включении даёт уменьшение тока и встроенного потенциала на каждом диоде (причём возможен сильный рост тока утечки из-за эффекта Дарлингтона), а также нелинейность температурных характеристик в зависимости от числа диодов [1]. Это особенно важно при защите цепей питания типа Vcc-Vccp, Vcc-Vss, где необходимо именно последовательное включение диодов. Ещё одним важным моментом является следующее: наиболее чувствительным к ESD элементом является n-МОП транзистор выходного буфера [1-5]. Во время ESD ток может распространяться неравномерно по всем каналам многозатворного транзистора (в силу названных выше причин), достигнуть критического значения It2, в результате чего устройство будет повреждено. Для предотвращения этого эффекта можно использовать элементы GCNMOS, а можно - резисторы на основе n-кармана. Таким образом, размеры этих элементов можно подобрать так, чтобы повреждения n-МОП транзистора не происходило. Если позволяет технология, то для экономии площади можно использовать pinch-резисторы [1].

Использование биполярных транзисторов в качестве элементов защиты от ESD не всегда возможно в КМОП-технологиях и более применимо к технологии БиКМОП. Вариант защиты с использованием биполярного транзистора представлен на рис. 7б [1].

Рисунок 7. Характеристика работы n-МОП транзистора (а); использование биполярного транзистора в качестве основного элемента, проводящего стрессовый ток (б)

В этом случае для быстрого включения биполярного транзистора во время ESD используются МОП-транзисторы. Принцип их действия схож с GCNMOS: благодаря паразитной ёмкости затвор–сток в первый момент ESD MP1 создаст достаточное напряжение на базе Q1 с помощью Rb. Важно правильно подобрать сопротивление Rb, чтобы Q1 не включался во время нормальной работы устройства и в тоже время обеспечивал включение во время ESD. Преимуществами данной схемы является малая длина пути стрессового разряда, что делает её более выносливой к ESD, и малая нагрузочная ёмкость выходного буфера благодаря использованию биполярного транзистора.

Использование МОП-транзисторов в качестве защитных устройств всегда основывается на эффекте его работы в snapback-режиме, что обеспечивает равномерное распределение тока после первого пробоя и недопущение температурного пробоя устройства [1-5].

Литература

- Sanjay Dabral, Timothy Maloney. BASIC ESD AND I/O DESIGN. Intel Corporation.

- Eihard Haseloff. Latch up, ESD, and other Phenomena. Texas Instruments. Application Report. May 2000.

- Gianluca Boselli. ON HIGH INJECTION MECHANIZMS IN SEMICONDUCTOR DEVICES UNDER esd CONDITIONS.

- Julian Zhiliang Chen, Ajith Amerasekera, Charvaka Duvvury. Design and Optimization of Gate-Driven NMOS ESD Protection Circuits in Submicron CMOS Processes. IEEE Trans. Electron Devices. Dec. 1998. Vol. 45. P. 2448.

- Ming-Dou Ker, Chung-Yu Wu. Complementary-SCR ESD Protection Circuit with Interdigitated Finger-Type Layout for Input Pads of Submicron CMOS IC’s. IEEE, Trans. Electron Devices. July 1995. Vol. 42. P. 1297.

- Ming-Dow Ker, Chung-Yu Wu. Complementary-LVTSCR ESD Protection Circuit for Submicron CMOS VLSI/ULS. IEEE, Trans. Electron Devices. April 1996. Vol. 43. № 4.

- Ming-Dow Ker, Hun-Hsien Chang, Chung-Yu Wu. A Gate-Coupled PTLSCR/NTLSCR ESD Protection Circuit for Deep-Submicron Low-Voltage CMOS IC’s. IEEE, J. Solid-State Circuits. January 1997. Vol. 32. № 1. P. 38.

- Ming-Dow Ker, Chung-Yu Wu, Tung-Yang Chen, Hun-Hsien Chang. ESD Protection Design on Analog Pin with Very Low Input Capacitance for High-Frequency or Current-Mode Applications. IEEE, J. Solid-State Circuits. Aug. 2000. Vol. 35. № 8. P. 1194.

- Stephen G. Beebe. Characterization, Modeling, and Design of ESD Protection Circuits. Technical report. Advanced Micro Devices. March 1998.

|