| |

Т. Солохина, Я. Петричкович, А. Глушков, Ю. Александров, В. Глушков, А. Семенович, А. Беляев, Ю. Грибов, В. Никольский, В. Силин, М. Алексеев, С. Бабичевский, В. Федин

Мультикор-12S - сигнальный контроллер с плавающей точкой для высокоточных встраиваемых применений

Как уже сообщалось (Chip News №7 2003 г.), ГУП НПЦ "ЭЛВИС" и центр проектирования ОАО "АНГСТРЕМ" завершили проектирование и успешно изготовили на зарубежной фабрике по 0,25-мкм технологии тестовые образцы первого отечественного сигнального контроллера миниконфигурации Мультикор-12S (MC-12S) с плавающей точкой для микроминиатюрных высокоточных встраиваемых применений. Мультикор-12S - это "система на кристалле", объединяющая на одном кристалле кремния два процессора: стандартный MIPS32 - совместимый контроллер и процессор цифровой обработки сигналов оригинальной архитектуры с плавающей точкой в формате IEEE754. Тестовые образцы данной микросхемы как первого прибора базовой серии Мультикор-12xx получены в июле 2003 г. Тактовая частота этих микросхем составляет 80 МГц. Микросхема размещена в корпусе QFP-208 и потребляет не более 1 Вт. Пиковая производительность DSP-ядра - 240 MFLOPs (IEEE754). Ожидается, что серийные образцы ИМС (МС-12xx) будут иметь производительность не менее 270–300 MFLOPs.

Мультикор-12xx - это базовая серия сигнальных контроллеров миниконфигурации с плавающей точкой для микроминиатюрных высокоточных встраиваемых применений. Новая интегральная микросхема (ИМС) содержит в своем составе стандартное RISC-ядро с системой команд MIPS32 и оригинальное, масштабируемое и программируемое ядро цифрового сигнального процессора с плавающей точкой - DSP-ядро (DSP - Digital Signal Processing) "ELcore12"TM (ELVEES’s core). DSP-ядро имеет 32-разрядную гарвардскую SISD- архитектуру (SISD - Single Instructions Single Data - один поток команд и один поток данных).

ИМС "Мультикор-12" сочетает в себе лучшее от обоих классов приборов: ИМС микроконтроллеров и ИМС цифровой обработки сигналов, что особенно важно для микроминиатюрных высокоточных встраиваемых применений, когда приходится решать в рамках ограниченных габаритов одновременно обе задачи: управления и обработки информации, включая сигналы и изображения.

Важное дополнительное качество новой для пользователя микросхемы - возможность выбора оптимального для данного применения режима обработки, сбалансированного между пиковой производительностью и динамическим диапазоном обрабатываемых данных. Форматы обработки варьируются от байтных форматов с фиксированной точкой до высокоточных: стандартного формата с плавающей точкой (IEEE754) или длинного плавающего формата 32E16.

Кроме того, для разработчика системы впервые обеспечена уникальная возможность применения новых алгоритмов принятия решений в RISC-ядре на основе параллельно выполняемых процедур адаптивного анализа и обработки сигналов в DSP-ядре, что реализуется в пределах одной и той же микросхемы, и, что особенно важно, для сверхминиатюрных применений.

Для этих целей разработаны методы применения RLS/LNS алгоритмов, в частности, для адаптивных антенных решеток на базе ИМС платформы "МУЛЬТИКОР", формируемые в виде пакета прикладных программ.

Однотактное исполнение практически всех инструкций в обоих процессорных ядрах, минимальные скалярные задержки для сложных вычислений, привычный стандартный синтаксис ассемблера для DSP-ядра при возможности глубокого управления ресурсами его операционного блока, пиковые производительности, измеряемые сотнями миллионов операций с плавающей точкой - факторы, призванные обеспечить широкое применение новой отечественной ИМС.

Кристалл ИМС MC-12S имеет размеры 5x5 мм и размещается в пластиковом корпусе QFP-208. Серийные образцы этих микросхем будут размещаться в отечественном металлокерамическом корпусе "Монополия-208", а также в зарубежных пластиковых корпусах типа QFP-208 и PBGA-256.

Основные технические характеристики тестовой ИМС сигнального микроконтроллера c плавающей точкой Мультикор-12S приведены в табл. 1.

Таблица 1. Основные технические характеристики тестовой ИМС сигнального микроконтроллера c плавающей точкой Мультикор-12S при нормальных условиях

|

Параметр

|

Значение параметра

|

|

Технология изготовления

|

Заказная КМОП СБИС, технологические нормы 0,25-мкм/5 металлов/3,3 В(периферия)/2,5 В (ядро)

|

|

Тактовая частота в нормальных условиях, МГц, не менее

|

80

|

|

RISC-ядро

|

32-разрядный MIPS32 совместимый процессор. Устройство управления памятью (MMU) на основе полностью ассоциативного буфера преобразования адресов (TLB), объемом 16 двойных ячеек. Поддержка ОС LINUX

|

|

DSP-ядро

|

Оригинальное ЦПОС ядро ELcore-12 с плавающей и фиксированной точкой SISD-архитектуры. Аппаратная реализация стандарта с плавающей точкой IEEE754

|

|

Число каналов DMA

|

10

|

|

Разрядность программируемых таймеров

|

32

|

|

Режимы энергосбережения

|

Несколько специальных архитектурных решений и режимов энергосбережения. Вход в режим программно, выход из режима по внешним прерываниям

|

|

Порт JTAG IEEE 1149.1, встроенные накристальные средства отладки

|

Тестирование и отладка программ

|

|

Производительность RISC-ядра, млн.оп./с, не менее

|

80

|

|

Пиковая производительность DSP-ядра при нормальной температуре, млн.оп./с, не менее

|

240 – 32b арифметических операций с плавающей точкой (IEEE754)

|

|

Объем внутреннего ОЗУ данных RISC-ядра

|

12 Кбайт

|

|

Объем кэш-команд RISC-ядра

|

2 Кбайт

|

|

Объем внутреннего ОЗУ данных DSP-ядра

|

8 Кбайт

|

|

Объем внутреннего ОЗУ программ DSP-ядра

|

8 Кбайт

|

|

Рассеиваемая мощность, мВт, не более

|

1000- максимальная;

800- при неработающем DSP-ядре (режим Stop);

75- при программном уменьшении тактовой частоты в 16 раз;

5- при программном отключении тактовой частоты

|

|

Порты

|

|

Порт UART 16550

|

|

Байтные порты

|

2 (совместимые с ADSP21160)

|

|

Последовательные порты

|

2 (совместимые с ADSP21160)

|

|

Порт памяти

|

поддержка статической памяти типа SRAM, FLASH, а также синхронной памяти типа SDRAM;

|

|

программное задание циклов ожидания;

|

|

4 внешних прерывания;

|

|

4 внешних запроса DMA

|

|

|

Система инструкций

|

RISC-ядро- архитектурно подобно MIPS32, включая аппаратно поддерживаемое умножение и деление. DSP-ядро- оригинальное. RISC-подобная система инструкций. Стандартный формат плавающей точки IEEE 754. Форматы фиксированной и программно поддерживаемой плавающей точки двойной точности

|

|

Корпус

|

QFP-208 (32x32 мм);

PBGA-256 (17x17 мм);

металлокерамический, 208 выводов ("Монополия-208", либо аналогичный ему)

|

В серийных образцах ИМС MC-12 планируется расширение внутренней памяти до 2 Мбит, а повышение тактовой частоты - до 90–100 МГц (будет уточнена по результатам измерений серийных образцов в I кв. 2004 г.). Кроме того, для этого типа ИМС, помимо QFP-208 (32x23 мм), планируется использование корпусов металлокерамического типа.

В микросхеме имеются несколько режимов энергосбережения:

- перевод DSP-ядра в режим Stop;

- программное изменение величины тактовой частоты;

- программное отключение тактовой частоты. Включение тактовой частоты осуществляется по внешним прерываниям.

ИМС МС-12S разработана как система на кристалле на базе платформы "МУЛЬТИКОР", является 32-разрядным высокопроизводительным устройством и включает два процессорных ядра в своем составе: RISC-ядро (центральный процессор) и сопроцессор цифровой обработки сигналов с фиксированной и плавающей точкой (DSP-ядро).

RISC-ядро является 32-разрядным процессором, имеющим архитектуру и систему команд, подобно MIPS32. RISC-ядро содержит устройство управления памятью (MMU) на основе полностью ассоциативного буфера преобразования адресов (TLB), объемом 16 двойных ячеек.

Система команд DSP-ядра является стандартной, не уступающей по функциональности ЦПОС семейства SHARC (ADI). В нём обеспечено однотактное исполнение практически всех команд. Поэтому все базовые процедуры сигнальной обработки (фильтровые, спектрально-корреляционные и др.), программируются достаточно просто, в отличие от некоторых специализированных процессоров сигналов с глубоким конвейером фазы обработки данных.

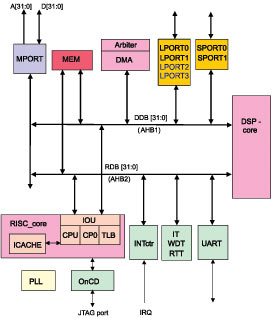

Структура микросхемы МС-12S приведена на рис. 1:

- процессорное RISC-ядро (RISC-core);

- процессорное ЦПОС-ядро (DSP-core); DSP-ядро (ELcore-12xx) - программируемое масштабируемое DSP-ядро сопроцессора-акселератора c плавающей точкой минимальной вычислительной мощности с архитектурой SISD (Single Instruction Single Data);

- ядро 10-канального контроллера DMA (Direct Memory Access);

- 32-разрядный порт памяти MPORT (Memory Port);

- ядро контроллера прерывания (INTctr - Interrupt controller);

- ядро 32-разрядного таймера (TIMER);

- ядро фазовой автоподстройки частоты (PLL);

- ядро интервального таймера - (IT);

- ядро сторожевого таймера (WDT);

- ядро таймера реального времени (RTT);

- встроенные средства отладки программ с интерфейсом JTAG OnCD (On Chip Debugger);

- внутренняя память (в серийных образцах составит не менее 2 Mбит):

- двухпортовое ОЗУ RISC-ядра объемом 12 Кбайт (RAM);

- КЭШ инструкций RISC-ядра (ICACHE) объемом 2 Кбайта;

- ОЗУ данных DSP-ядра объемом 8 Кбайт;

- ОЗУ программ DSP-ядра объемом 8 Кбайт;

- внешние интерфейсы:

- A(31:0) - шина адреса порта внешней памяти;

- D(31:0) - шина данных порта внешней памяти;

- UART - универсальный асинхронный порт;

- 2 последовательных порта (совместимых с портами ADSP21160, ADI);

- 2 линковых порта (совместимых с портами ADSP21160, ADI);

- внутренние интерфейсы (на базе стандартных шин AMBA):

- RDB(31:0) - шина данных RISC-ядра;

- DDB(31:0) - шина данных DMA

Рисунок 1. Структура МС-12S

Шины передачи данных RDB и DDB реализованы в соответствии со спецификацией шины AHB (Advanced High-performance Bus) архитектуры AMBA (Advanced Microcontroller Bus Architecture).

RISC-ядро является ведущим в двухпроцессорной конфигурации и выполняет основную программу. Для RISC-ядра обеспечен доступ к следующим ресурсам DSP-ядра, являющегося ведомым по отношению к RISC-ядру: обмен данными RISC-ядра с ресурсами DSP-ядра выполняется по командам LOAD, STORE. Память DSP-ядра и его регистры для RISC-ядра 32-разрядные (словные), то есть состояние двух младших разрядов адреса игнорируется.

RISC-ядро управляет работой DSP-ядра посредством передачи ему задания (макрокоманды) с последующим запуском DSP-ядра (перевод из режима STOP в режим RUN). С другой стороны, DSP-ядро формирует следующие прерывания в RISC-ядро:

- программное;

- по переполнению стека;

- при выполнении команды STOP;

- при достижении адреса останова при исполнении программы до адреса останова или завершении требуемого числа шагов при пошаговом исполнении программы.

Назначение и функции выводов микросхемы МС-12S

Мультикор-12S имеет следующие типы выводов:

- порт внешней памяти - 89;

- управление - 20;

- 2 последовательных порта - 12;

- 2 линковых порта - 20;

- UART - 6;

- электропитание - 32.

Описание выводов MC-12 приведено в табл. 2-7.

Таблица 2. Порт внешней памяти

|

Название вывода

|

Количество

|

Тип

|

Назначение

|

|

A[31:0]

|

32

|

O

|

Шина адреса

|

|

D[31:0]

|

32

|

IO

|

Шина данных

|

|

nWR[3:0]

|

4

|

O

|

Запись байтов асинхронной памяти

|

|

nWE

|

1

|

O

|

Запись асинхронной памяти

|

|

nRD

|

1

|

O

|

Чтение асинхронной памяти

|

|

nACK

|

1

|

I

|

Готовность асинхронной памяти

|

|

nCS[3:0]

|

4

|

O

|

Разрешение выборки банков памяти

|

|

SRAS

|

1

|

O

|

Строб адреса строки

|

|

SCAS

|

1

|

O

|

Строб адреса колонки

|

|

SWE

|

1

|

O

|

Разрешение записи

|

|

DQM[3:0]

|

4

|

O

|

Маска выборки байта

|

|

SCLK

|

1

|

O

|

Тактовая частота работы

|

|

CKE

|

1

|

O

|

Разрешение частоты

|

|

A10

|

1

|

O

|

10 разряд адреса

|

|

BA[1:0]

|

2

|

O

|

Номер банка

|

|

nFLYBY

|

1

|

O

|

Признак режима передачи DMA "Flyby"

|

|

nOE

|

1

|

O

|

Разрешение чтения внешнего устройства

|

|

Всего 89 выводов

|

Таблица 3. Управление

|

Название вывода

|

Количество

|

Тип

|

Назначение

|

|

nDMAR[3:0]

|

4

|

I

|

Запрос канала DMA

|

|

NMI

|

1

|

I

|

Немаскируемое прерывание

|

|

nIRQ[3:0]

|

4

|

I

|

Запросы прерывания

|

|

BYTE

|

1

|

I

|

Разрядность шины данных сегмента 3 внешней памяти:

0–32 разряда;

1–8 разрядов

|

|

PLL_EN

|

1

|

I

|

Разрешение работы PLL

|

|

XTI, XTO

|

1

|

I,O

|

Сигнал тактовой частоты

|

|

RTC_XTI

|

1

|

I

|

Сигналы частоты реального времени

|

|

nRST

|

1

|

I

|

Сигнал установки исходного состояния

|

|

|

|

TCK

|

1

|

I

|

Тестовый тактовый сигнал (JTAG)

|

|

TRST

|

1

|

I

|

Установка исходного состояния (JTAG)

|

|

TMS

|

1

|

I

|

Выбор режима теста (JTAG)

|

|

TDI

|

1

|

I

|

Вход данных теста (JTAG)

|

|

TDO

|

1

|

0

|

Выход данных теста (JTAG)

|

|

Всего 20 выводов

|

Таблица 4. Последовательные порты (2 штуки)

|

Название вывода

|

Количество

|

Тип

|

Назначение

|

|

DT

|

1

|

O

|

Передаваемые данные

|

|

DR

|

1

|

I

|

Принимаемые данные

|

|

TCLK

|

1

|

IO

|

Частота передачи

|

|

RCLK

|

1

|

IO

|

Частота приема

|

|

TFS

|

1

|

IO

|

Синхронизация передачи

|

|

RFS

|

1

|

IO

|

Синхронизация приема

|

|

Всего 6x2 = 12 выводов

|

Таблица 5. Линковые порты (2 штуки)

|

Наименование сигнала

|

Количество

|

Тип

|

Назначение

|

|

LDAT

|

8

|

IO

|

Шина данных

|

|

LCLK

|

1

|

IO

|

Синхронизация

|

|

LACK

|

1

|

IO

|

Подтверждение

|

|

Всего 10x2 = 20 выводов

|

Таблица 6. UART

|

Наименование сигнала

|

Количество

|

Тип

|

Назначение

|

|

SIN

|

1

|

I

|

Вход последовательных данных

|

|

SOUT

|

1

|

O

|

Выход последовательных данных

|

|

NDTR

|

1

|

O

|

Готовность UART к установлению связи (Data Terminal Ready)

|

|

NRTS

|

1

|

O

|

Готовность UART к обмену данными (Request To Send)

|

|

NCTS

|

1

|

I

|

Готовность модема к обмену данными (Clear To Send)

|

|

NDSR

|

1

|

I

|

Готовность модема к установлению связи (Data Set Ready)

|

|

Всего 6 выводов

|

Таблица 7. Электропитание

|

Название вывода

|

Количество

|

Тип

|

Назначение

|

|

VDD

|

7

|

I

|

Напряжение электропитания ядра

|

|

DVDD

|

8

|

I

|

Напряжение электропитания выходных драйверов

|

|

PVDD

|

1

|

I

|

Напряжение электропитания PLL

|

|

GND

|

15

|

I

|

Земля ядра, входных и выходных драйверов

|

|

PGND

|

1

|

I

|

Земля PLL

|

|

Всего 32 вывода

|

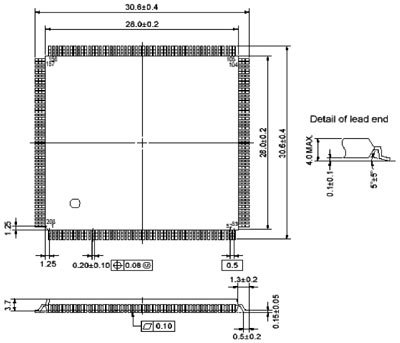

На рис. 2 представлен чертеж корпуса ИМС МС-12S (QFP-208).

Рисунок 2. Чертеж корпуса микросхемы MC-12S

Нумерация выводов микросхемы MC-12S в корпусе QFP-208 приведена в табл. 8.

Таблица 8. Нумерация выводов MC-12S в корпусе QFP-208

|

Номер вывода

|

Название вывода

|

Номер вывода

|

Название вывода

|

Номер вывода

|

Название вывода

|

Номер вывода

|

Название вывода

|

|

1

|

-

|

53

|

-

|

105

|

-

|

157

|

-

|

|

2

|

-

|

54

|

-

|

106

|

-

|

158

|

-

|

|

3

|

-

|

55

|

-

|

107

|

-

|

159

|

-

|

|

4

|

A[31]

|

56

|

D[26]

|

108

|

nCS[0]

|

160

|

DR0

|

|

5

|

A[30]

|

57

|

D[25]

|

109

|

SRAS

|

161

|

TCLK0

|

|

6

|

A[29]

|

58

|

D[24]

|

110

|

SCAS

|

162

|

RCLK0

|

|

7

|

A[28]

|

59

|

D[23]

|

111

|

SWE

|

163

|

TFS0

|

|

8

|

A[27]

|

60

|

D[22]

|

112

|

DQM[3]

|

164

|

RFS0

|

|

9

|

PVDD

|

61

|

VDD

|

113

|

VDD

|

165

|

VDD

|

|

10

|

PGND

|

62

|

GND

|

114

|

GND

|

166

|

GND

|

|

11

|

A[26]

|

63

|

D[21]

|

115

|

DQM[2]

|

167

|

DT1

|

|

12

|

A[25]

|

64

|

D[20]

|

116

|

DQM[1]

|

168

|

DR1

|

|

13

|

A[24]

|

65

|

D[19]

|

117

|

DQM[0]

|

169

|

TCLK1

|

|

14

|

A[23]

|

66

|

D[18]

|

118

|

SCLK

|

170

|

RCLK1

|

|

15

|

A[22]

|

67

|

D[17]

|

119

|

CKE

|

171

|

TFS1

|

|

16

|

A[21]

|

68

|

D[16]

|

120

|

A10

|

172

|

RFS1

|

|

17

|

A[20]

|

69

|

D[15]

|

121

|

BA[1]

|

173

|

LDAT0[7

|

|

18

|

A[19

|

70

|

D[14]

|

122

|

BA[0]

|

174

|

LDAT0[6]

|

|

19

|

A[18]

|

71

|

D[13

|

123

|

nFLYBY

|

175

|

LDAT0[5]

|

|

20

|

VDD

|

72

|

PVDD

|

124

|

PVDD

|

176

|

VDD

|

|

21

|

GND

|

73

|

PGND

|

125

|

PGND

|

177

|

GND

|

|

22

|

A[17]

|

74

|

D[12]

|

126

|

nOE

|

178

|

LDAT0[4]

|

|

23

|

A[16]

|

75

|

D[11]

|

127

|

nDMAR[3]

|

179

|

LDAT0[3]

|

|

24

|

A[15]

|

76

|

D[10]

|

128

|

nDMAR[2]

|

180

|

LDAT0[2]

|

|

25

|

A[14]

|

77

|

D[9]

|

129

|

nDMAR[1]

|

181

|

LDAT0[1]

|

|

26

|

A[13]

|

78

|

D[8]

|

130

|

nDMAR[0]

|

182

|

LDAT0[0]

|

|

27

|

A[12]

|

79

|

D[7]

|

131

|

NMI

|

183

|

LCLK0

|

|

28

|

A[11]

|

80

|

D[6]

|

132

|

nIRQ[3]

|

184

|

LACK0

|

|

29

|

A[10]

|

81

|

D[5]

|

133

|

nIRQ[2]

|

185

|

LDAT1[7]

|

|

30

|

A[9]

|

82

|

D[4]

|

134

|

nIRQ[1]

|

186

|

LDAT1[6]

|

|

31

|

PVDD

|

83

|

VDD

|

135

|

AVDD

|

187

|

PVDD

|

|

32

|

PGND

|

84

|

GND

|

136

|

AGND

|

188

|

PGND

|

|

33

|

A[8]

|

85

|

D[3]

|

137

|

nIRQ[0]

|

189

|

LDAT1[5]

|

|

34

|

A[7]

|

86

|

D[2]

|

138

|

BYTE

|

190

|

LDAT1[4]

|

|

35

|

A[6]

|

87

|

D[1]

|

139

|

PLL_EN

|

191

|

LDAT1[3]

|

|

36

|

A[5]

|

88

|

D[0]

|

140

|

XTI

|

192

|

LDAT1[2]

|

|

37

|

A[4]

|

89

|

nWR[3]

|

141

|

XTO

|

193

|

LDAT1[1]

|

|

38

|

A[3]

|

90

|

nWR[2]

|

142

|

RTCXTI

|

194

|

LDAT1[0]

|

|

39

|

A[2]

|

91

|

nWR[1]

|

143

|

PLL_OUT

|

195

|

LCLK1

|

|

40

|

A[1]

|

92

|

nWR[0]

|

144

|

nRST

|

196

|

LACK1

|

|

41

|

A[0]

|

93

|

nWE

|

145

|

TCK

|

197

|

SIN

|

|

42

|

PVDD

|

94

|

PVDD

|

146

|

VDD

|

198

|

VDD

|

|

43

|

PGND

|

95

|

PGND

|

147

|

GND

|

199

|

GND

|

|

44

|

D[31]

|

96

|

nRD

|

148

|

TRST

|

200

|

SOUT

|

|

45

|

D[30]

|

97

|

nACK

|

149

|

TMS

|

201

|

nDTR

|

|

46

|

D[29]

|

98

|

nCS[3]

|

150

|

TDI

|

202

|

nRTS

|

|

47

|

D[28]

|

99

|

nCS[2]

|

151

|

TDO

|

203

|

nCTS

|

|

48

|

D[27]

|

100

|

nCS[1]

|

152

|

DT0

|

204

|

nDSR

|

|

49

|

-

|

101

|

-

|

153

|

-

|

205

|

nDSR

|

|

50

|

-

|

102

|

-

|

154

|

-

|

206

|

-

|

|

21

|

-

|

103

|

-

|

155

|

-

|

207

|

-

|

|

52

|

-

|

104

|

-

|

156

|

-

|

208

|

-

|

Архитектура RISC-ядра

RISC-ядро является 32-разрядным процессором с архитектурой, подобной стандартной архитектуре MIPS32. Его системой команд является система команд MIPS32 ISA (Instruction Set Architecture).

RISC-ядро содержит устройство управления памятью (MMU) на основе полностью ассоциативного буфера преобразования адресов (TLB), объемом 16 двойных ячеек.

Реализация конвейера RISC-ядра аналогична микропроцессору R3000A (IDT).

Управление памятью (Memory Management)

RISC-ядро поддерживает три режима работы:

- режим User;

- режим Kernel;

- режим Debug.

Режим User используется для прикладных программ.

Режим Kernel обычно используется для обработки исключений и для выполнения привилегированных системных функций, включая управление сопроцессором CP0.

Режим Debug используется для отладки программного обеспечения совместно с JTAG-отладчиком. В данном режиме RISC-ядро остановлено. Режим Debug реализован аппаратно. RISC-ядро не поддерживает функций EJTAG MIPS32, которые являются дополнительными, не обязательными для реализации. Карта виртуальной памяти RISC-ядра аналогична MIPS32. RISC-ядро не поддерживает программного режима Debug, поэтому сегмента dseg не существует.

Преобразование виртуальных адресов в физические выполняется в режимах FM (Fixed Mapped) и TLB подобно MIPS32 4K. Режим преобразования определяется состоянием бита FM системного регистра CSR.

RISC-ядро содержит полностью ассоциативный буфер TLB (Translation Look aside Buffer) объемом 16 двойных ячеек. Размер страницы может изменяться от 4 Кбайт до 16 Мбайт.

КЭШ программ (ICACHE)

Кэш программ RISC-ядра (ICACHE) имеет следующие основные характеристики:

- direct-mapped;

- индексирование по физическому адресу;

- контроль по физическому Тэгу;

- длина строки - 16 байт (4 32-разрядных слова);

- бит действительности (valid) бит для каждой строки;

- объем - 2 КБайт (16 КБайт - в серийной микросхеме).

Регистры сопроцессора CP0

В табл. 9 приведен перечень регистров сопроцессора CP0, реализованных в RISC-ядре.

Таблица 9. Перечень регистров сопроцессора CP0, реализованных в RISC-ядре

|

Условное обозначение

|

Назначение

|

|

Index

|

Индекс для матрицы TLB

|

|

Random

|

Индекс для матрицы TLB, сгенерированный случайным образом

|

|

EntryLo0

|

Младшая часть вхождения TLB для четных виртуальных страниц

|

|

EntryLo1

|

Младшая часть вхождения TLB для нечетных виртуальных страниц

|

|

Context

|

Указатель на PTE

|

|

PageMask

|

Управление размером страницы во вхождениях TLB

|

|

Wired

|

Управление номером фиксированных вхождений TLB

|

|

BadVAddr

|

Содержит адрес для последнего, адресно-связанного исключения

|

|

Count

|

Счетчик процессорных циклов

|

|

EntryHi

|

Старшая часть вхождения TLB

|

|

Compare

|

Управление прерыванием от таймера

|

|

Status

|

Регистр состояния

|

|

Cause

|

Код причины последнего исключения

|

|

EPC

|

Виртуальный адрес команды (состояние программного счетчика PC), вызвавшей исключени

|

|

PRId

|

Идентификатор версии процессора

|

|

Config

|

Конфигурационный регистр

|

|

Config1

|

Конфигурационный регистр 1

|

|

LLAddr

|

Содержит физический адрес, по которому выполняется последняя команда LL

|

|

ErrorEPC

|

Содержит состояние PC в момент возникновения последнего исключения по ошибке

|

Обработка исключений

В RISC-ядре обработка исключений выполняется подобно MIPS32.

RISC-ядро поддерживает следующие типы исключений:

- Reset (установка исходного состояния), NMI (немаскируемое прерывание), маскируемое прерывание;

- исключения по выполнению команд SYSCALL, BREAK;

- исключения, связанные с TLB: Machine Check, TLB miss, TLB Mod;

- неправильное формирование адреса;

- арифметическое переполнение, выполнение резервной команды.

Система команд

RISC-ядро реализует следующие типы команд (всего 100 команд):

- команды обмена данными с памятью Load, Store (15 команд);

- арифметические и логические команды (26 команд);

- команды умножения и деления, в том числе умножение с накоплением (13 команд);

- команды Branch, Jump (20 команд);

- команды управления сопроцессором CP0 (8 команд);

- специальные команды SYSCALL, BREAK, ERET, TRAP и т.д. (18 команд).

Особенности обработки данных в форматах с плавающей точкой в DSP-ядре

DSP-ядро МС-12 имеет расширенные возможности по динамическому диапазону обрабатываемых данных, позволяющие обрабатывать данные в 8/16/32-разрядных форматах с фиксированной точкой, либо в одном из форматов с плавающей точкой - 24Е8 (стандарт IEEE 754) или 32Е16 (расширенный формат с плавающей точкой) - и осуществлять при этом компромиссный выбор между точностью и производительностью. Основной формат плавающей точки 24E8 полностью поддерживается аппаратно, расширенный - программно и аппаратно.

32-разрядный формат с плавающей точкой 24E8

32-разрядный формат с плавающей точкой 24E8 соответствует спецификации IEEE-754 и имеет следующий вид:

где s - знак числа (используется прямой код со знаком); e - экспонента числа со смещением +127; f - дробная часть мантиссы числа.

Численное значение числа в формате плавающей точки:

X = (-1)s·2E·F,

где E = e-127 - экспонента без смещения; F = 1,0 + f/223 - полная мантисса. F  1,0, то есть мантисса может быть только нормализованной. Бит, соответствующий 1,0, "умалчивается". 1,0, то есть мантисса может быть только нормализованной. Бит, соответствующий 1,0, "умалчивается".

В табл. 10 приведены команды для обработки основного формата плавающей точки 24E8.

Таблица 10. Команды для обработки основного формата плавающей точки 24E8

|

№

|

Команда

|

Признаки

N Z V

|

Пояснение

|

|

1

|

FTST S

|

+ + +

|

Формирование признаков числа S

|

|

2

|

FMPY S1,S2,D

|

+ + +

|

Перемножение D = S1·S2

|

|

3

|

FADD S1,S2,D

|

+ + +

|

Сложение D = S1+S2

|

|

4

|

FSUB S1,S2,D

|

+ + +

|

Вычитание D = S2–S1

|

|

5

|

FAS S1,S2,D

|

+ + +

|

Сложение и вычитание: D = S2+S1, S2новое = S2–S1

|

|

6

|

FINT S,D

|

+ + +

|

Округление S к ближайшему целому числу (для остатка 0,5 - к четному), запись в D в формате плавающей точки

|

|

7

|

FLOOR S,D

|

+ + +

|

Округление S к ближайшему целому снизу, запись в D в формате плавающей точки

|

|

8

|

CVFI S,D

|

+ + +

|

Преобразование формата числа из плавающей точки (S) в целочисленный 32-разр. в дополнительном коде (D)

|

|

9

|

CVIF S,D

|

+ + -

|

Преобразование формата числа из целочисленного 32-разр. в дополнительном коде (S) в плавающую точку (D)

|

|

10

|

FIN S,D

|

+ + +

|

0-я итерация обратной величины D = 1,0/S

|

|

11

|

FINR S,D

|

+ + +

|

0-я итерация обратной величины от квадратного корня D = 1,0/

|

Примечания.

- Команды FMPY, FIN, FINR выполняются в блоке умножения, остальные - в арифметическом блоке, что должно учитываться при формировании параллельных операций.

- Округление к ближайшему целому снизу соответствует стандартному режиму округления к -бесконечности.

Пример программирования обработки в формате плавающей точки 24Е8 - Гильберт-фильтрация

Гильберт-фильтрация - формирование квадратурной компоненты действительного сигнала (врезка).

Врезка

|

|

|

CLRL R8

|

(A0)+I0,R2

|

(AT)+IT,R0

|

Сброс Q

|

Загрузка X, G

|

|

|

FMPY R0,R2,R4

|

|

(A0)+I0,R2

|

(AT)+IT,R0

|

P=X*G

|

Загрузка X, G

|

|

|

DO 30,Lg

|

|

|

|

Цикл по 30

|

|

|

Lg:

|

FMPY R0,R2,R4

|

FADD R4,R8,R8

|

(A0)+I0,R2

|

(AT)+IT,R0

|

P=X*G Q=Q+P

|

Загрузка X, G

|

|

|

FMPY R0,R2,R4

|

FADD R4,R8,R8

|

|

|

P=X*G Q=Q+P

|

Загрузка X, G

|

|

|

|

FADD R4,R8,R8

|

R10,(A0)+

|

|

Q=Q+P

|

Ввод Х

|

|

|

|

|

MOVE R8,(A1)+

|

|

Запись результата Q

|

|

|

STOP

|

|

|

|

|

|

|

Входной сигнал (X) вводится по 1-му отсчету после каждого цикла фильтрации и хранится в 64-элементном кольцевом буфере.

Полный отклик фильтра Гильберта имеет 64 коэффициента, из них половина - ненулевых. Они хранятся в 32-элементном кольцевом буфере (G).

Результаты фильтрации накапливаются в выходном линейном буфере (Q).

Массив X адресуется генератором А0 c индексом I0 = 2 (для пропуска нулевых коэффициентов отклика) и модульным регистром M0 = 63, обеспечивающим циклическую адресацию буфера.

Массив G адресуется генератором AT с индексом IT = 1 и модульным регистром MT = 31.

Массив Q адресуется генератором A1 c единичным инкрементом.

Вычисления выполняются в формате плавающей точки.

Чтение отсчетов X и G, перемножение (P = XґG) и накопление произведений (Q = Q+P) выполняются за один такт. Поэтому главный программный цикл состоит из одной параллельной команды.

Начальная задержка вычислений - 3 такта. Быстродействие - 1 такт на ненулевой отвод фильтра.

Расширенный формат с плавающей точкой (32E16)

DSP-ядро программно-аппаратным способом поддерживает также обработку чисел в расширенном формате плавающей точки 32E16.

Формат с плавающей точкой размещается в 32-разрядном слове (мантисса F) и в 16-разрядном слове (экспонента Е):

Мантисса F: 32-разрядное число в дробном формате в дополнительном коде. Нормальное состояние мантиссы - нормализованное.

Экспонента E: 16-разрядное целое число в дополнительном коде.

Численное значение числа в формате плавающей точки:

X = 2E·F.

В табл. 11 приведен параметр продолжительности (в числе тактов) выполнения арифметических операций в формате расширенной плавающей точки 32Е16.

Таблица 11. Продолжительность выполнения арифметических операций в формате расширенной плавающей точки 32Е16

|

Операция в формате 32Е16

|

Число тактов

|

|

Сложение

|

5

3 (без нормализации результата)

|

|

Вычитание

|

6

5 (без округления)

4 (без нормализации результата)

3 (без округления и нормализации)

|

|

Сложение и вычитание одной пары операндов

|

9

8 (без округления)

5 (без нормализации результата)

4 (без округления и нормализации)

|

|

Умножение

|

4

2 (без нормализации результата)

|

Порт JTAG и встроенные аппаратные средства отладки программ

Сигнальный микроконтроллер МС-12S имеет встроенные аппаратные средства отладки OnCD (On Chip Debugger), доступ к которым производится через JTAG-порт, реализованный в полном соответствии со стандартом IEEE 1149.1 (IEEE Standard Test Access Port and Boundary-Scan Architecture).

OnCD предоставляет пользователю возможность по заданным через JTAG-порт условиям остановить:

- RISC-ядро, при этом по завершении выполнения в RISC текущей команды останавливаются все активные компоненты МС-12, такие как DSP и DMA;

- DSP-ядро с возможностью продолжения работы или остановки RISC-ядра.

В качестве условий останова RISC-ядра могут быть:

- обращение к памяти по записи или по чтению информации в заданном диапазоне адресов или при совпадении с заданными двумя адресами;

- выполнение команд с адресами в заданном диапазоне или при совпадении с заданными двумя адресами;

- выполнение команды с заданным адресом или обращение к памяти по записи или по чтению информации по заданному адресу;

- вызов исполняемой программой любого из заданных векторов исключений (прерываний) или их совокупности;

- выполнение специальной команды перехода МС-12 в отладочный режим;

- выполнение заданного числа команд;

- останов DSP;

- требование перехода в отладочный режим со стороны JTAG-порта.

В свою очередь, условиями останова DSP-процессора могут быть:

- выполнение команды с заданным адресом;

- выполнение заданного числа команд.

После останова RISC-ядра или DSP-ядра имеется возможность с помощью OnCD визуализировать (или изменить) состояние всех архитектурных элементов MC-12, которые проецируются во всём адресном пространстве памяти системы или доступны посредством выполнения команд в RISC-процессоре в режиме kernel, и продолжить выполнение программы:

- только в RISC-процессоре при остановленном DSP;

- только DSP при остановленном RISC-процессоре;

- совместное выполнение программ RISC и DSP.

Перечисленные условия останова МС-12S, возможность в режиме отладки выполнения команды RISC по одному такту продвижения команды в конвейере, а также доступность всего адресного пространства в состоянии останова, дают возможность использовать OnCD и JTAG-порт для построения эффективных отладчиков программ и систем.

OnCD имеет программный интерфейс (JTAG-отладчик) с интегрированной средой разработки и отладки программ MC-12S. Это позволяет проводить разработку программного обеспечения в реальном масштабе времени.

Фотография отладочной платы для микросхемы Мультикор-12S приведена на рис. 3.

Рисунок 3. Отладочная плата для ИМС MC-12

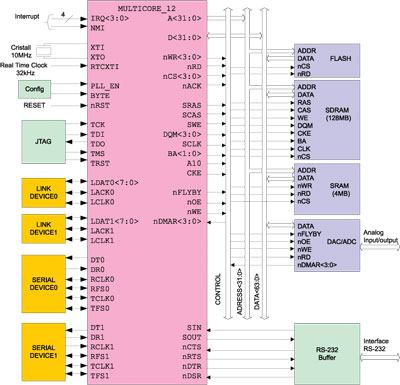

На рис. 4 приведена типовая схема применения ИМС Мультикор-12.

Рисунок 4. Типовая схема применения ИМС Мультикор-12

На рис. 4 использованы следующие обозначения:

- FLASH - постоянное запоминающее устройство типа FLASH;

- SDRAM - синхронное динамическое оперативное запоминающее устройство (ОЗУ);

- SRAM - статическое ОЗУ;

- Interrupt - запросы прерывания;

- DAC/ADC - цифро-аналоговые и аналого-цифровые преобразователи;

- LINK DEVICE - устройства, подключаемые к линковым портам;

- SERIAL DEVICE - устройства, подключаемые к последовательным портам;

- RS-232 Buffer - приемо-передатчики RS-232;

- Config - схема задания конфигурации;

- RESET - узел формирования сигнала установки исходного состояния.

MC-12XX не только не уступает по своим возможностям лучшим зарубежным ИМС с плавающей точкой, но и превосходит их при сопоставлении по типовым процедурам сигнальной обработки c фиксированной и плавающей точкой (табл. 12 и 13).

Таблица 13. Сравнение цифровых сигнальных контроллеров с плавающей точкой миниконфигурации MC-12XX, мидиконфигурации МС-02xx и MC-Fxx (ГУП НПЦ "ЭЛВИС") с цифровыми процессорами сигналов семейства SHARC ADSP-21160N и TigerSHARC TS201 (ADI)

|

Формат плавающей точки, стандарт IEEE 754

|

MC-12xx 100 МГц 0,25-мкм/2,5 В *)

|

MC-02xx 100 МГц 0,25-мкм/2,5 В

|

MC-Fxx 200 МГц 0,25-мкм/2,5 В *)

|

ADSP- 21160N 95 МГц 0,18-мкм/1,8 В

|

Tiger SHARC TS201 600 МГц 0,13-мкм/1,2 В

|

|

Пиковая производительность

|

300 MFLOP/s

|

1200 MFLOP/s

|

2400 MFLOP/s

|

570 MFLOP/s

|

3600 MFLOP/s

|

|

БПФ-1024, комплексное, формат плавающей точки стандарт IEEE 754

|

210 мкс

|

53 мкс

|

26,5 мкс

|

97 мкс

|

16,77 мкс

|

|

БПФ-256, комплексное, формат плавающей точки стандарт IEEE 754

|

44 мкс

|

11 мкс

|

5,5 мкс

|

|

|

|

БПФ-256, комплексное, формат (16+j16), блочная плавающая точка

|

21 мкс

|

5,3 мкс

|

2,7 мкс

|

|

|

|

Свертка (MAC-процедура), IEEE 754

|

100 MMAC/s

|

400 MMAC/s

|

800 MMAC/s

|

190 MMAC/s

|

|

|

Нерекурсивный фильтр (на отвод)

|

10 нс

|

2,5 нс

|

1,25 нс

|

5,2 нс

|

0,83 нс

|

|

Нерекурсивный комплексный фильтр (на отвод)

|

40 нс

|

10 нс

|

5 нс

|

5,2 нс

|

3,33 нс

|

|

Рекурсивный фильтр (на биквадратное звено)

|

40 нс

|

10 нс

|

5 нс

|

21 нс

|

2,33 мкс

|

| Матричное умножение: |

| [3x3]*[3x1] |

90 нс |

23 нс |

11 нс |

47 нс |

|

| [4x4]*[4x1] |

160 нс |

40 нс |

20 нс |

83 нс |

|

| [8x8]*[8x8] |

5,6 мкс |

1,4 мкс |

0,7 мкс |

|

|

|

|

Деление (y/x)

|

100 нс

|

25 нс

|

12,5 нс

|

31 нс

|

|

|

Обратная величина квадратному корню

|

120 нс

|

30 нс

|

15 нс

|

47 нс

|

|

|

Декодер Витерби, на одну метрику пути, 16b формат

|

10 нс

|

2,5 нс

|

1,25 нс

|

|

|

|

БП Уолша – Адамара -256, комплексное, формат (16+j16), блочная плавающая точка

|

11 мкс

|

3 мкс

|

1,5 мкс

|

|

|

*) ожидаемые предварительные параметры для нормальных условий эксплуатации. Будут уточнены по результатам измерений серийных образцов ИМС в I кв. 2004 г.

Сравнение DSP-ядра "ELcore-14" (в составе ИМС МС-12xx) и TMS320C54x (ТI) выполнено в табл. 12.

Как показывают результаты предварительных синтезов для перспективной модификации ИМС серии "Мультикор" МС-Fxx для 0,25-мкм и 0,18-мкм технологий, её реализация даже по 0,25-мкм технологии и, тем более, по 0,18-мкм технологии (с дополнительной архитектурной модификацией DSP-ядра) позволит получить характеристики, сравнимые с ИМС TigerSHARC TS201 (600 МГц/ 0,13-мкм/1,2 В).

Важно отметить, что при этом не будет использован 12-уровневый конвейер, реализованный в ИМС TigerSHARC TS201, что обеспечивает ещё дополнительные резервы для модификации ИМС MC-Fxx.

Об этой же самой возможности достижения высоких характеристик для ИМС серии "Мультикор", по сравнению с зарубежными аналогами, реализованными на одну ступень лучшей технологии (к примеру, 0,18-мкм к 0,25-мкм), свидетельствует и другое сравнение в приведенной выше таблице. Оно выполнено для ИМС MC-02xx (100 МГц/0,25-мкм /2,5 В) разработки ГУП НПЦ "ЭЛВИС" и ADSP-21160N (95 МГц/0,18-мкм /1,8 В) разработки ADI.

Средства разработки и отладки программ ИМС платформы "МУЛЬТИКОР"

В состав инструментального программного обеспечения платформы "МУЛЬТИКОР" входят:

- интегрированная среда разработки и отладки программ под OS WIN/LINUX ("MCStudio");

- компилятор языка С, ассемблеры RISC- и DSP-ядер, линковщики и программные утилиты;

- программный симулятор ИМС;

- отладчик, обеспечивающий отладку на языке программы и в коде RISC- и DSP-ядер на симуляторе или через JTAG на прототипе или ИМС.

Software Development Kit (SDK) для разработки пользовательских систем на базе ИМС платформы "Мультикор"

В состав SDK (рис. 5) входят:

- плата модуля эмулятора сигнальных контроллеров "Мультикор" МС-11xx /12xx/23xx/01xx/02xx с файлами Virtex-конфигураций серий; программный драйвер модуля работает под ОС Windows®NT/LINUX;

- источник электропитания типа ATX;

- кабель для подключения модуля к параллельному порту персонального компьютера (PC);

- кабель для подключения модуля к последовательному порту PC (RS-232C);

- кабель для загрузки конфигурации в ПЛИС;

- CDROM с документацией.

Рисунок 5. SDK платформы «МУЛЬТИКОР»

Содержимое CDROM:

- интегрированная среда разработки и отладки программ "MCStudio" под ОС Windows®NT/LINUX;

- инструкция по эксплуатации MCStudio;

- руководство программиста MCStudio;

- руководство системного программиста;

- набор системных и прикладных библиотек базовой конфигурации;

- модуль эмулятора Centaurus 2K2. Инструкция по эксплуатации;

- Bitfile прототипа ИМС серии Мультикор-хх (по договоренности);

- процессорное ядро RISCorE32-xx. Руководство пользователя;

- процессорное ядро RISCorE32-xx. Система команд;

- процессорное ядро ELcore-xx. Система команд;

- процессорное ядро ELcore-xx. Руководство пользователя.

Цена поставляемого комплекта SDK - договорная. В стоимость поставки включается двухдневный курс обучения двух специалистов Заказчика работе с SDK c предоставлением им возможности проживания в гостинице г. Зеленограда на период обучения.

Следующие перспективные разработки ИМС "Мультикор" с плавающей точкой - базовые серии сигнальных контроллеров мидиконфигурации с плавающей точкой МС-24xx и серия МС-02xx для высокопроизводительных и высокоточных систем обработки информации.

В состав ИМС обеих серий входит ядро "ELcore-14xx" - программируемое масштабируемое DSP-ядро сопроцессора-акселератора, аналогичное использованному в ИМС МС-12xx. Ядро обеспечивает эффективную обработку данных не только в формате с плавающей, но и с фиксированной точкой.

В связи с решением протестировать ядро DSP с плавающей точкой на приборе минимальной конфигурации, а также с заказами от нескольких десятков фирм на использование, в первую очередь, ИМС МС-12xx, запланированный запуск для получения тестовых образцов МС-02S был передвинут разработчиками на несколько месяцев вперед.

Однако успешное изготовление образцов ИМС МС-12S позволяет планировать получение серийных образцов в I квартале 2004 года для другой ИМС с плавающей точкой - МС-24xx, так как ИМС МС-12S является тестовой как для ИМС МС-24xx, так и для ИМС MC-02xx.

Ожидаемая производительность ИМС МС-24xx составит около 600 млн. операций с плавающей точкой в секунду в формате IEEE754, а её структура соответствует 2SIMD-расширению ядра "ELcore-14xx".

Можно также, не дожидаясь серийных образцов ИМС МС-12xx/MC-24xx/MC-02xx, использовать Инструментальное ПО ИМС серий "Мультикор" и с его помощью успешно отлаживать прикладные пользовательские программы, сразу ориентированные на перспективную отечественную элементную базу.

Такую возможность предоставляют программные Симуляторы или Virtex-прототипы чипов, тем более, что демонстрационной версией МСStudio воспользовались уже почти 70 российских фирм. CD с МСStudio доступен бесплатно всем желающим, а условия его получения - по контактному адресу.

Все сказанное позволяет начинать уже сегодня проектирование принципиально новой отечественной РЭА на базе импортозамещающих базовых отечественных серий ИМС "Мультикор", среди которых первая - ИМС "Мультикор-12xx" - миниконфигурация двухпроцессорного однокристального сигнального контроллера с плавающей точкой.

|