| |

К. Жучков, С. Хоружий, Е. Чепель

Сравнительный анализ производительности процессоров для задач цифровой обработки сигналов

В статье рассматриваются тестирование и сравнительный анализ производительности процессоров, применяемых при решении задач цифровой обработки сигналов (ЦОС). Предлагаются альтернативные варианты построения комплекса ЦОС на базе процессоров с описанием преимуществ и недостатков каждого варианта. Приводятся результаты сравнения производительности процессоров при решении задач фильтрации, спектрального и корреляционного анализа.

Введение

Традиционно, задачи цифровой обработки сигналов реального времени, для которых требуются значительные вычислительные мощности (спектральный анализ, корреляция, демодуляция, декодирование и др.) решались и решаются с помощью модулей ЦОС, содержащих высокопроизводительные сигнальные процессоры и ПЛИС. Такой подход позволяет высокую скорость потока данных оставить до ЭВМ, и предоставить последней заниматься свойственными ей функциями: ведением баз данных, статистической обработкой, выводом информации на монитор и печать и т.п. При этом разработчику модуля ЦОС приходится решать непростые задачи выбора ПЛИС (Xilinx, Altera и др.) и сигнального процессора (Texas Instruments, Analog Devices, Motorola и др.), а также распределения алгоритма ЦОС между ними. Таким образом, задача оптимизации реализации проекта при фиксированном алгоритме ЦОС уже является многопараметрической.

Успехи последних лет в области процессоров со сложным набором инструкций (Complex Instruction Set Computer - CISC), которые демонстрировали компании Intel и AMD, и появление библиотек функций цифровой обработки сигналов, оптимизированных под архитектуру этих процессоров, например Intel Integrated Performance Primitives (IIPP), добавили ещё одну степень свободы при выборе вариантов построения комплекса ЦОС. Однако подход, основанный на применении в качестве платформы ЦОС CISC-процессора, требует высоких скоростей ввода данных в память ЭВМ (например, через PCI). Немаловажным оказывается и тот факт, что для добавления ещё одного канала обработки приходится вместо компактного модуля ставить целых два компьютера и локальную вычислительную сеть для решения задач сопряжения между каналами, так как процессор компьютера обработки работает на максимуме свой производительности и ничего кроме решения задачи ЦОС делать не успевает. Стоимость такого комплекса при увеличении количества каналов обработки растет отнюдь не в арифметической прогрессии.

В настоящее время имеются публикации, например [1-3], в которых проводится сравнение производительности CISC и различных цифровых сигнальных процессоров при выполнении конкретных математических операций (FIR- фильтры, быстрое преобразование Фурье, БПФ, и т.п.). Результатом таких сравнений является вывод о том, что последнее поколение процессоров Intel незначительно уступает последнему поколению процессоров TI. При таком тестировании не учитываются накладные расходы, связанные, например, с получением данных, а измеряется лишь время выполнения функции ЦОС, что является некорректным, так как при решении реальных задач ЦОС неучет влияния шины на скорость процессора недопустим. Целью настоящей работы является проведение сравнения производительности CISC и цифровых сигнальных процессоров в рамках реального комплекса ЦОС при решении ими одинаковых задач.

Альтернативные варианты построения комплекса ЦОС

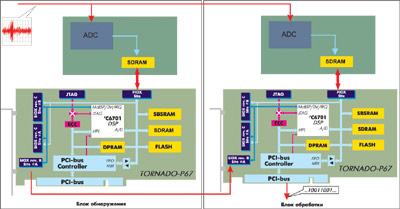

В качестве задачи, на примере которой можно провести сравнение вариантов построения комплекса ЦОС, выберем реализацию канала приема с быстродействующей цифровой обработкой входного потока принимаемых сигналов в реальном времени для обнаружения импульсов сигналов и сосредоточением всей обработки по разработанным алгоритмам именно этих участков сигналов. Сравнительный анализ производительности CISC и цифровых сигнальных процессоров проводится для трех возможных вариантов построения комплекса ЦОС, решающих поставленную задачу. Рассматриваемые варианты комплексов ЦОС отличаются типом процессора, используемого в блоке обработки. Такой подход при инвариантных алгоритмах обработки позволяет обеспечить одинаковые условия использования процессоров. При рассмотрении каждого варианта построения комплекса ЦОС можно выделить два блока: блок обнаружения и блок обработки. Блок обнаружения строится на базе модуля с цифровым процессором обработки сигналов TMS320C6701 и модуля АЦП на базе ПЛИС Хilinx Virtex II с буфером объемом 8 млн. отсчетов и остается неизменным для каждого варианта.

В качестве первого варианта блока обработки предлагается схема комплекса ЦОС, построенного на базе цифрового сигнального процессора TMS320C6701 как процессора обработки, представленная на рис. 1. С выхода приемника сигнал поступает на входы АЦП обнаружения и обработки. После аналого-цифрового преобразования сигнал синхронно записывается во внутренний буфер как АЦП обнаружения, так и АЦП обработки. Обнаружение радиоимпульса во входном потоке данных происходит в модуле цифровой обработки сигналов TORNADO-P6701 (TP6701) компании "МикроЛАБ Системс" (http:\\www.mlabsys.com) на базе цифрового сигнального процессора TMS320C6701. Модули ЦОС TORNADO представляют собой очень удобный "конструктор ЦОС", включающий в себя динамическую (SDRAM), синхронную блоковую (SBSRAM), двухпортовую (DPRAM) память, а также последовательный (SIOX) и параллельный (PIOX) интерфейсы ввода/вывода. При обнаружении радиоимпульса передается целеуказание в аналогичный модуль DSP TP6701 посредством мультиканального последовательного буферизованного порта (McBSP), используя интерфейс SIOX. При получении целеуказания производится считывание данных (временных отсчетов) из буфера АЦП обработки посредством интерфейса PIOX (рис. 1). Алгоритмы обнаружения, оптимизированные для процессора С6000, достаточно полно изложены в работе [4]. В DSP обработки проводится регистрация фрагмента сигнала с обнаруженным импульсом и его обработка по приведенным ниже алгоритмам.

Рисунок 1. Схема комплекса ЦОС на базе процессора обработки TMS320C6701 (первый вариант)

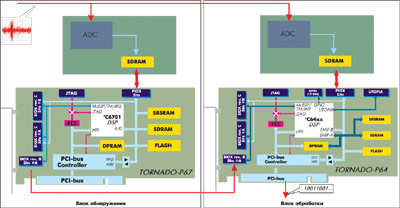

Второй вариант схемы комплекса ЦОС на базе процессора TMS320C6416 получен путем замены в предыдущей схеме (рис. 1) модуля TP67 на TP64. Схема данного комплекса ЦОС представлена на рис. 3. C учетом того, что архитектура внутренней и внешней периферии процессора претерпела изменения при трансформации от С6701 к С6416, различие в модулях сводится не только к замене процессора. Отдельно стоит отметить использование различных шин (EMIF A и EMIF B) для подключения внешней памяти и интерфейсов. Алгоритм работы комплекса ЦОС в этом варианте подобен предыдущему. Получение целеуказаний от подсистемы обнаружения осуществляется посредством одного из McBSP. Чтение данных из буфера АЦП подсистемы обработки производится через интерфейс PIOX. Далее проводится обработка обнаруженного импульса в DSP обработки.

Рисунок 2. Система ЦОС TORNADO-P6416

Рисунок 3. Схема комплекса ЦОС на базе процессора TMS320C6416 (второй вариант)

Наконец, в третьем варианте построения комплекса ЦОС, представленном на рис. 4, в блоке обработки используется центральный процессор Host-машины. В данном варианте построения комплекса при обнаружении радиоимпульса, посредством шины PCI, подсистемой обнаружения передается целеуказание в подсистему обработки. При получении целеуказания, производится считывание данных (временных отсчетов) из буфера АЦП обработки через шину PCI в ОЗУ Host-машины (рис. 4). В рассматриваемом варианте построения комплекса обработка полученных из АЦП данных проводится центральным процессором Host-машины. В качестве Host-машины в данном варианте реализации комплекса ЦОС используется сервер на базе материнской платы (Intel SE7501BR2) с двумя процессорами Intel Xeon 2,4 ГГц - 1 ГБайт оперативной памяти DDR 266.

Рисунок 4. Схема комплекса ЦОС на базе процессора обработки Intel Xeon (третий вариант)

Тестирование и сравнительный анализ

Для того чтобы исключить вопросы, связанные с оптимальностью реализации кода для того или иного процессора, мы при тестировании производительности остановили свой выбор на алгоритмах, которые, с одной стороны, целиком реализованы в виде функций библиотек разработчиков процессоров, а с другой стороны, вполне могут быть использованы как самостоятельные алгоритмы ЦОС для получения конкретных радиотехнических характеристик сигнала. В качестве таких алгоритмов выбраны оптимальная фильтрация с использованием FIR-фильтра, спектральный анализ с помощью БПФ, корреляционный анализ с помощью функции взаимной корреляции.

Для альтернативных вариантов построения комплекса ЦОС проводился сравнительный анализ производительности процессоров обработки сигналов. С целью такого анализа измерялось время вычисления работы FIR-фильтра с 35 отводами по 1024 отсчетам буфера с реализацией сигнала, вычисления БПФ 1024 комплексных отсчетов сигнала и расчет корреляционной функции 1024-точечного сигнального буфера и 1024-точечного массива отсчетов шаблонной функции. Здесь важно отметить, что работа процессоров обработки сигналов происходила параллельно с передачей данных: через интерфейс PIOX посредством канала прямого доступа к памяти (DMA) в случае первого и второго вариантов построения комплекса ЦОС и посредством режима "BUSMASTER" контроллера PCI - в третьем варианте.

Результаты проведенного тестирования и измерения времени выполнения программ по описанным алгоритмам приведены в таблице. Причем функции, реализующие перечисленные выше математические операции, взяты из специализированных библиотек для соответствующих процессоров: DSPLIB фирмы TI для процессоров TMS320C6000 и Intel Integrated Performance Primitives 3.0 для процессоров Intel. Функции этих библиотек оптимизированы под архитектуру конкретного цифрового сигнального процессора.

Представленные результаты сравнения производительности процессоров в таблице показывают, что, во-первых, специализированная архитектура цифрового сигнального процессора TMS320C6416, которая обеспечивает оптимальное вычисление математических операций, характерных для цифровой обработки сигналов, позволяет решать задачи ЦОС эффективнее, нежели архитектура CISC-процессора (сравним тактовые частоты 600 МГц и 2,4 ГГц). Во-вторых, доступ к памяти посредством канала DMA у процессоров TMS320C6000 не влияет на скорость их работы, в то время как производительность пары процессоров Intel Xeon падает почти в два раза. Можно также отметить существенный прогресс в области цифровых сигнальных процессоров при переходе от С6701 с тактовой частотой 166 МГц к С6416 с тактовой частотой 600 МГц. Генеральная линия Texas Instruments, нацеленная на тактовую частоту 1,1 ГГц, подтверждает перспективность использования семейства С64xx.

Заключение

Представлены три варианта построения комплекса ЦОС, отличающиеся процессором обработки сигналов (C6701, C6416, Intel Xeon). Проведено сравнение производительности процессоров обработки сигналов в рамках представленных вариантов на примере решения задач фильтрации, спектрального и корреляционного анализа. Результаты измерений показали, что производительность комплекса ЦОС на базе процессора TMS320C6416 практически в два раза выше производительности комплекса с двумя процессорами Intel Xeon.

Таблица. Результаты тестирования процессоров обработки сигналов

|

|

TMS320C6701-166 МГц

|

TMS320C6416-600 МГц

|

Intel Xeon – 2,4 ГГц

|

|

При передаче данных

|

Без передачи данных

|

При передаче данных

|

Без передачи данных

|

При передаче данных

|

Без передачи данных

|

|

Корреляционная функция (1024 x 1024)

|

27 мс

|

27 мс

|

1,7 мс

|

1,7 мс

|

4,3 мс

|

2,5 мс

|

|

БПФ 1024 комплексных точки

|

160 мкс

|

160 мкс

|

11 мкс

|

11 мкс

|

25 мкс

|

18 мкс

|

|

FIR-фильтр с 35 отводами

|

393 мкс

|

393 мкс

|

25,7 мкс

|

25,7 мкс

|

62 мкс

|

36 мкс

|

Литература

- Дорохин С.А. Высокопроизводительные процессоры цифровой обработки сигналов 2000 г. // Цифровая обработка сигналов. 1999. № 1. С. 59–65.

- Данилов А. Современные цифровые процессоры обработки сигналов // Электронные компоненты. 2003. № 4. С. 23–34.

- Трубин Вл., Трубин Вит. Анатомия DSP // Электронные компоненты. 2003. № 4. С. 17–20.

- Жучков К., Хоружий С. Реализация эффективных алгоритмов обнаружения и обработки на цифровом сигнальном процессоре платформы TMS320C6000 // Chip News. 2003. № 4. С. 20–23.

|