С. Волков, А. Ефишин, С. Морозов, С. Соколов

Проблема электростатического разряда и современные методы защиты интегральных схем от него. Часть 2

Примеры схемотехнических и технологических реализаций схем защиты от ESD

Для субмикронных технологий с применением силицидов в качестве контактов при использовании технологии слабого подлегирования областей стока и истока (Lightly-Doped Drain, LDD) особенно важно обеспечить равномерное распределение стрессового тока после пробоя, своевременное включение защитного элемента и быстрый отвод тока с наименьшим рассеиванием тепла. Схема защиты должна иметь минимальное паразитное сопротивление и емкость, чтобы минимизировать падение напряжения на этом элементе и уменьшить дополнительную нагрузочную емкость защищаемого устройства в случае её использования в выходном буфере.

Всего этого можно добиться различными путями, один из которых - совмещение в защитном элементе управляемого диода с низким напряжением защелкивания (Low-Voltage-Threshold Silicon-Controlled Rectifier, LVTSCR) и n-МОП транзистора с затвором, связанным с контактной площадкой через конденсатор (Gate-Coupled NMOS, GCNMOS). Использование LVTSCR позволяет минимизировать площадь защитного элемента, снижает напряжение защелкивания до напряжения вступления в низкоомную область n-МОП транзистора входного/выходного буфера. Использование этого варианта обеспечивает равномерное распределение тока после защелкивания, что дела-ет возможным использование такого элемента в силицидных технологиях. GCNMOS не стоит использовать как основной элемент ESD-защиты, так как для пропускания большого стрессового тока через устройство необходимо делать его слишком большим по сравнению, например, с SCR.

Описание устройства GC-NTLSCR/PTLSCR

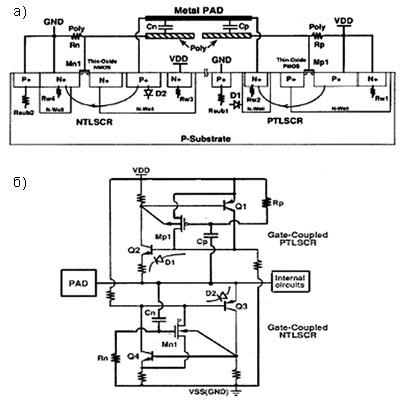

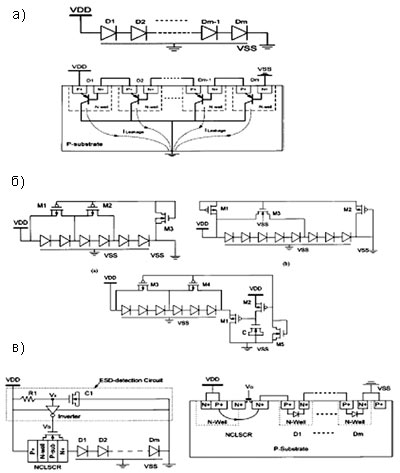

Реализация защитного элемента, объединяющего SCR и GCNMOS, представлена на рис. 1a [2].

Рисунок 1. Элемент защиты входного/выходного буфера, основанного на объединении LVTSCR и GCNMOS (а); структура PTLSCR NTLSCR с затвором, связанным с защищаемой контактной площадкой через конденсатор (б)

На рис. 1б представлена комплементарная защита входной/выходной площадки с помощью LVTSCR n- и p-типа. Затворы n-МОП и p-МОП связаны с контактной площадкой через конденсаторы Cn и Cp, образованные поликремнием и самой контактной площадкой. Поэтому создание конденсаторов не требует дополнительного пространства, что является большим преимуществом. Напряжения защелкивания двух управляемых диодов равны напряжениям пробоя между диффузионной n+ областью и подложкой и диффузионной p+ областью и n-карманом для NTLSCR и PLTSCR, соответственно. Это напряжение соответствует напряжению вступления в snapback-область ВАХ для n-МОП и p-МОП. Использование n-кармана дополнительно к n+ диффузии для катодов NTLSCR и PTLSCR увеличивает эффективность соответствующих эмиттеров, то есть позволяет пропускать через устройство больший стрессовый ток.

Для субмикронных технологий напряжение защелкивания сравнимо с напряжением пробоя окисла, что может привести к повреждению окисла до защелкивания. Конденсаторы Cn и Cp, связанные с затворами, подбирают для установки значение напряжения защелкивания. Для поддержания напряжения на затворе на заданном уровне в течение определенного времени, используются поликремниевые резисторы Rn и Rp, представляющие собой совместно с Cn и Cp RC-цепи.

Как видно из схемы, представленной на рис. 1a, в структуре устройства имеются паразитные диоды D1 и D2, образованные p-диффузией и n-карманом в NTLSCR и n-карманом и p-подложкой в PTLSCR. Эти диоды улучшают защитные характеристики данного элемента. Также показаны паразитные сопротивления карманов и подложки.

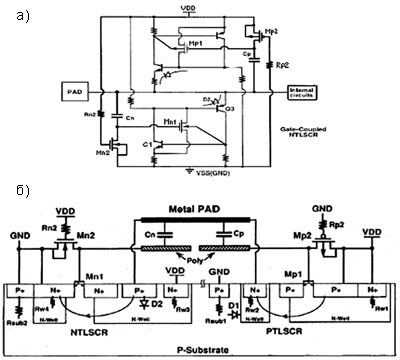

На рис. 1б, резисторы Rn и Rp реализуются с помощью поликремния, что достаточно удобно для технологий, в которых используется высокоомный поликремний, так как номиналы этих резисторов должны быть порядка десятков-сотен кОм. Но для технологий, в которых сопротивление поликремния около 3–4 Ом/ , его использование непрактично для создания резисторов. Здесь используются дополнительные длинноканальные транзисторы Mn2 и Mp2. Схема и структура модифицированного устройства представлена на рис. 2a и б. , его использование непрактично для создания резисторов. Здесь используются дополнительные длинноканальные транзисторы Mn2 и Mp2. Схема и структура модифицированного устройства представлена на рис. 2a и б.

Рисунок 2. Модифицированная схема устройства GC PTLSCR NTLSCR защиты контактной площадки (а); структура модифицированного устройства GC PTLSCR NTLSCR (б)

Сглаживание напряжения реализуется с помощью транзисторов Mn2 и Mp2, подключенных стоком к контактной площадке. Резисторы Rn2 и Rp2 имеют небольшие номиналы, выполняются в поликремнии и обеспечивают время задержки ESD-стресса на затворах Mn2 и Mp2 при возникновении стрессового напряжения на шине питания или шине земли.

Принцип работы устройства GC-NTLSCR/PTLSCR

При нормальных условиях работы транзистор Mn2 открыт и напряжение на затворе Mn1 равно Vss, то есть Mn1 закрыт. Транзистор Mp2 также открыт и передает на затвор Mp1 напряжение Vdd. Таким образом, защитное устройство гарантированно выключено при нормальных условиях. Паразитные диоды D1 и D2 обеспечивают включение защитного устройства при условиях: напряжение ESD < Vss – 0,6V и напряжение ESD > Vdd + 0,6V.

При возникновении ESD на контактной площадке стрессовый ток может пойти различными путями в зависимости от полярности напряжения на контактной площадке. Для PS-режима (когда ESD положительно по отношению к Vss, а контактная площадка Vdd оборвана) стрессовый ток покидает схему через шину земли, при этом на затворе Mn1 возникает положительное напряжение ESD, которое включает его. После включения Mn1 защелкивается NTLSCR. После защелкивания на контактной площадке поддерживается напряжение порядка 1–2 В, что обеспечивает полную защиту подзатворного окисла транзисторов входного буфера.

Для NS-режима (когда ESD отрицательно по отношению к шине земли) и PD-режима (когда ESD положительно по отношению к шине питания) диоды D1 и D2 положительно смещены и пропускают весь стрессовый ток. Отрицательное (положительное) стрессовое напряжение на контактной площадке фиксируется уровнем -0,6 ~ -0,8 В (0,6 ~ 0,8 В). Это также обеспечивает полную защиту подзатворного окисла транзисторов входного буфера. Данная паразитная диодная структура обеспечивает хорошую пропускную способность стрессового тока.

Для ND-режима (Vdd заземлен, Vss не зафиксирован) на затворе Mp1 возникает отрицательное стрессовое напряжение через конденсатор Cp. Это напряжение включает Mp1, который в свою очередь защелкивает PTLSCR. После защелкивания напряжение на контактной площадке составляет ~1–2 В, что также обеспечивает защиту подзатворного окисла.

Следует отметить, что для ND (PS)-режимов ESD-стресс может передаться через диод D2 (D1) и паразитный резистор Rw3 (Rsub1) на неподключенную шину питания ещё до того, как весь стрессовый ток будет выведен за пределы схемы. Это также может произойти через p-МОП элемент выходного буфера, размещенный между контактной площадкой и незафиксированной шиной питания. В этом случае может произойти преждевременное включение транзистора Mn2 (Mp2). Чтобы этого не происходило, между базой Mn2 (Mp2) и Vdd (Vss) включается поликремниевый резистор малого номинала Rn2 (Rp2), обеспечивающий задержку включения Mn2 (Mp2). Необходимо учесть, что дополнительное время задержки дает паразитная емкость между шинами питания. После включения Mn2 (Mp2) работает как резистор, создавая тем самым RC-цепь. Длина канала увеличивается для получения большего сопротивления. Время полного включения NTLSCR (PTLSCR) зависит от тока стока Mn1 (Mp1), который зависит от напряжения на затворе транзистора. Чем больше ток стока, тем быстрее включится устройство. Контролируя напряжение на затворе с помощью конденсатора Cn (Cp) и увеличивая время задержки включения Mn2 (Mp2), можно добиться оптимального быстродействия устройства. Конденсатор Cn (Cp) подбирается таким образом, чтобы обеспечить напряжение на затворе Mn1 (Mp1) ниже порогового для нормальных условий работы защищаемого устройства и выше порогового в случае ESD, то есть элемент защиты не должен включаться от возможных шумов.

Характеристики GC-NTLSCR/PTLSCR устройства защиты

Устройство было разработано для 0,6-мкм КМОП-технологии [2]. Размеры транзисторов Mn1 и Mp1 (ширина/длина, W/L) 75/1,0 мкм. Связывающие конденсаторы Cn и Cp имеют емкость 0,4 пФ, размеры транзисторов Mn2 и Mp2 - 10/10 мкм. Подробное описание тестирования устройства представлено в [2]. Согласно этим данным, HBM ESD более 8 кВ, а MM ESD в среднем - не ниже 600 В. Эти характеристики ESD-защиты превосходят существующие требования в сертификациях.

Описание элемента PDNMOS

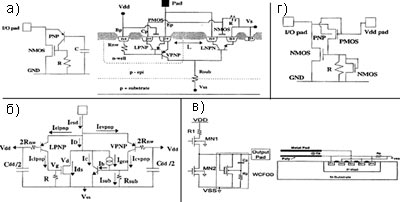

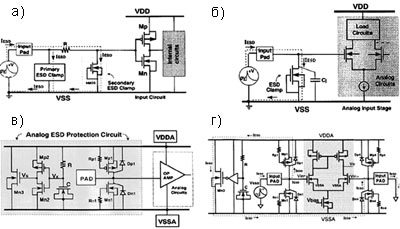

На рис. 3a представлена схема и структура n-МОП транзистора с заземленным затвором, управляемого латеральным паразитным pnp-транзистором (pnp Driven NMOS, PDNMOS) [1].

Рисунок 3. Схема и структура элемента PDNMOS (а); эквивалентная схема PDNMOS (б); схема модифицированного PDNMOS (в); схема и структура устройства WCFOD (г)

При нормальных условиях работы pnp-транзистор закрыт, а в случае ESD он открывается, и разряд передается через коллектор на базу n-МОП. Падение напряжения на резисторе R создает на затворе дополнительное увеличение напряжения, позволяющее быстрее включить элемент защиты.

Использование латерального pnp-транзистора позволяет снизить напряжение защелкивания устройства до значения Vsb-напряжения вступления в snapback-область ВАХ n-МОП транзистора. Емкость конденсатора должна быть достаточно большой, чтобы обеспечить подходящий коллекторный ток. Таким образом, меняя емкость конденсатора, мы изменяем потенциал на затворе n-МОП. Конденсатор может быть реализован с помощью паразитной емкости шины питания, если она достаточно велика. Если этой емкости недостаточно, необходимо ввести в структуру конденсатор.

Структура устройства приведена для субмикронной КМОП-технологии. Паразитный латеральный pnp-транзистор создается с помощью p-МОП транзистора. Длина канала p-МОП должна быть минимальна, чтобы увеличить эффективность биполярного транзистора. Как видно из рисунка, в структуре присутствует также паразитный вертикальный pnp-транзистор, который улучшает работоспособность устройства при ESD, так как способствует проведению стрессового тока.

Эквивалентная схема устройства представлена на рис. 3б [1].

Модифицированная схема PDNMOS

Если работа PDNMOS основывается на паразитной емкости шины питания, которая обеспечивает базовый ток pnp-транзистора, то быстродействие данной защитной структуры есть функция от этой емкости. В работе [1] было показано, что для стандартной емкости шины питания 100–200 пФ, имеющей место в смешанных схемах, устройство сохраняет работоспособность при напряжениях до 6,5 кВ для HBM.

Выносливость устройства к ESD уменьшается с уменьшением паразитной емкости шины питания, так как напряжение на затворе n-МОП Vd недостаточно для генерации значительного тока IDS, необходимого для быстрого защелкивания паразитных npn-транзисторов всех каналов (ток Icvpnp тоже низок из-за маленького базового тока). Также важно, что при слишком больших значениях паразитной емкости наблюдается некоторое снижение характеристик защищенности по ESD, так как для больших значений напряжения на затворе величина тока термического пробоя падает. Оптимальная величина напряжения на затворе n-МОП составляет около 3 В.

Для устройств с низкой паразитной емкостью шины питания необходимы дополнительные меры по улучшению защищенности схемы от ESD. Можно увеличить размер pnp-транзистора и номинал резистора, что значительно увеличит напряжение на затворе n-МОП. В случае слишком большой паразитной емкости необходимо использовать дополнительные фиксирующие диоды, которые ограничивали бы напряжение на затворе n-МОП транзистора. В качестве диодов можно использовать обычные диоды, реализуемые в n-кармане, или диодные включения n-МОП транзисторов (соединены области стока и затвора), в зависимости от технологии и области применения устройства. На рис. 3г показано устройство PDNMOS c фиксирующим n-МОП в диодном включении.

Характеристики PDNMOS устройства

Схема защиты от ESD PDNMOS была успешно применена в силицидной и обычной технологиях. Схема, показанная на рис. 3в, была реализована в силицидной 0,8-мкм технологии. Размер n-МОП транзистора (W/L) - 1000/0,8 мкм, p-МОП - 100/0,8 мкм, n-МОП c диодным включением - 150/0,8 мкм, номинал резистора, реализованного в n-кармане, - 15 кОм. Устройство проводит ток до 2,8 А при напряжении на контактной площадке 10 В. Ток термического пробоя - 3,2 мА/мкм. Выносливость устройства к ESD составляет 9 кВ для HBM.

Описание устройства WCFOD

Стоки транзисторов выходного буфера в КМОП-технологии часто непосредственно соединены с выходной контактной площадкой, что делает транзисторы выходного буфера более чувствительными к ESD. Ниже рассмотрен защитный элемент, состоящий из n-МОП транзистора с толстым подзатворным окислом, причем карман, в котором этот элемент выполнен, соединен с контактной площадкой через конденсатор (Well-Coupled Field-Oxide Device, WCFOD) [3]. На рис. 3в представлена схема и структура данного устройства.

n-МОП транзистор с полевым окислом в качестве подзатворного диэлектрика формируется n+ диффузиями, близко расположенными друг к другу в p-кармане. p-карман, в котором выполнено это устройство, подсоединен к земле через резистор Rp. Конденсатор Cp расположен в цепи, соединяющей этот карман с выходной контактной площадкой, чтобы управлять защелкиванием защитного элемента в случае ESD. Выходной буфер включает в себя нагрузочный n-МОП транзистор MN1 и согласующий n-МОП транзистор MN2. Резистор R1 номиналом 30 Ом подключен к шине питания. Он нужен для ограничения тока короткого замыкания во время переходного процесса.

Работа устройства WCFOD

Рассмотрим четыре режима возникновения ESD. Устройство наиболее уязвимо при подаче положительного стрессового напряжения на контактную площадку при оборванном напряжении шины питания (PS-режим), так как в этом случае происходит пробой в выходном n-МОП транзисторе со структурой LDD. В работе [3] отмечено, что выносливость к ESD у выходного буфера для PS-режима около 1 кВ, тогда как в NS-режиме устройство сохраняет работоспособность при 8 кВ стрессового напряжения для той же модели. Поэтому наиболее важно в первую очередь обеспечить защиту именно для PS-режима.

Для ESD, возникающем при PS-режиме, положительное стрессовое напряжение связано с p-карманом через конденсатор Cp. Это стрессовое напряжение поддерживается на кармане в течение времени, определенного RC-цепочкой Rp-Cp. Благодаря положительному напряжению на p-кармане, переход карман – исток элемента TFO открыт. Это приводит к более быстрому срабатыванию TFO (включению паразитного латерального npn-транзистора). Таким образом, можно обеспечить полное включение WCFOD для проведения стрессового тока ещё до того, как будет поврежден транзистор выходного буфера. Конденсатор Cp может быть реализован с помощью поликремния, помещенного под металлизацию выходного контакта, как это показано на рис. 3в. Тем самым конденсатор Cp не использует дополнительной площади. Поддерживающий резистор Rp может быть реализован в виде поликремния вокруг контактной площадки. Значения Cp и Rp должны обеспечивать выключенное состояние WCFOD при нормальных условиях работы и его включение в случае PS-режима электростатического разряда.

Характеристики WCFOD-устройства

Для оценки эффективности разработанного устройства была использована интегральная схема SRAM с напряжением питания 5 В, изготовленная по 0,5-мкм КМОП-технологии с n-подложкой и процессом LDD. Площадь поликремния под металлом составляет 88x88 мкм2, соответствующая емкость конденсатора Cp = 0,86 пФ. Резистор Rp реализован в поликремнии длиной 400 мкм вокруг контактной площадки, его сопротивление 24 кОм. Напряжение защелкивания WCFOD около 8 В. Этого достаточно для обеспечения защиты выходного буфера. Выносливость к ESD для PS-режима достигает 6,5 кВ для HBM [3].

Самонастраивающаяся схема защиты на диодах Зенера

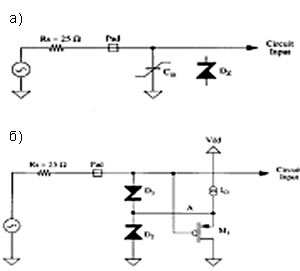

Главной причиной искажения входного сигнала в высокоскоростных аналоговых схемах является нелинейная зависимость входной емкости от поданного напряжения, которая связана со схемой входной защиты от ESD. Нелинейность входной емкости возникает из-за обратносмещенного pn-перехода. Эта нелинейная емкость вместе с конечным сопротивлением источника представляет собой фильтр низких частот, существенно влияющий на входной сигнал. Искажения достаточно сильны даже для относительно невысоких частот входного сигнала. Стандартная схема защиты таких ИС представляет собой диод Зенера.

Такая схема была протестирована на устройстве АЦП (Аналогово-Цифровой Преобразователь) с напряжением питания 5 В, реализованная в 0,8-мкм КМОП-технологии. Сигнал защищаемого аналогового входа ограничен диапазоном 0–2 В. Стандартная схема защиты - это диод Зенера с емкостью обратно смещенного перехода от 2 до 4 пФ (для напряжения обратного смещения - от 0 до 2 В). Эквивалентная схема показана на рис. 4а, где Rs - сопротивление источника и Cin - нелинейная емкость. Эта схема показана на рис. 4б.

Рисунок 4

Как видно из рисунка, два диода Зенера включены последовательно в противоположных направлениях. В случае возникновения на контактной площадке ESD любой полярности один из диодов Зенера открыт, на другом возникает пробой pn-перехода. Средняя точка А управляется источником тока на p-МОП транзисторе (M1).

Уменьшение искажения входного сигнала происходит по двум причинам. Во-первых, диапазон напряжений на диоде D1 меньше, чем в первом случае, что приводит к меньшему изменению емкости на переходе. Во-вторых, емкость D1 является самонастраивающейся, что также уменьшает искажение входного сигнала. Эти два механизма позволяют существенно снизить искажение сигнала. Опорный ток I0 = 300 мкА был выбран для обеспечения достаточно широкой полосы пропускания и скорости нарастания напряжения на диоде. Тестирование устройства при худших условиях (медленные модели, высокая температура) показало уровень искажения в 84 дБ, что на 20 дБ лучше, чем в стандартной схеме.

Схема защиты между контактными площадками шин питания

Даже очень хорошая защита контактных площадок входных и выходных сигналов не всегда может обеспечить полную защиту устройства от ESD. Между контактными площадками шин питания, а также между входами и выходами ИС может возникнуть стрессовое напряжение. Для этих ситуаций в структуру устройства необходимо ввести дополнительные элементы ESD-защиты между шинами питания. Самым простым решением является использование последовательно включенных диодов. Схема и структура такого защитного элемента изображена на рис. 5а.

Рисунок 5. Структура стандартной защиты в виде диодной цепочки (а); схемы включения диодной цепочки (б); схема и структура NCLSCR, объединенного с диодной цепочкой (в)

Чтобы уменьшить ток утечки в диодной цепочке, предпринимается ряд мер. Для обеспечения линейной зависимости блокирующего напряжения можно использовать одну из трех схем включения диодной цепочки, изображенных на рис. 5б [4].

В первом включении транзисторы M1 и М2 обеспечивают опорные токи в точках диодной цепочки.

Транзистор M3 включается как резистивная нагрузка. Аналогичным образом работает вторая схема. Транзисторы M1 и M2 всегда включены. Когда напряжение на истоке М3 меньше напряжения на затворе и их разница больше порогового напряжения, он открывается и дает дополнительный ток. В третьем случае диодная цепочка блокирована от Vss во время нормальной работы устройства, что позволяет избежать эффекта Дарлингтона среди паразитных pnp-транзисторов в цепочке, и таким образом уменьшить ток утечки в подложку.

Очень низкого значения тока утечки можно добиться с помощью объединения диодной цепочки и управляемого диода с низким напряжением защелкивания (n-МОП controlled lateral SCR, NCLSCR) [4]. Схема и структура такого устройства показана на рис. 5в.

В начале диодной цепочки помещается управляемый диод для блокировки тока утечки от Vdd к Vss через диодную цепочку. Дополнительно, NCLSCR имеет очень хорошие характеристики по быстродействию в случае ESD. Во время ESD он быстро защелкивается и передает стрессовый ток в диодную цепочку. Чтобы достичь этого, используется специальная схема определения электростатического разряда, основанная на RC-цепочке. Номинал резистора подбирается таким образом (tdelay = 0,1 – 1,0 мкс), чтобы обеспечить включение устройства только при стрессовых условиях.

Описание работы устройства NCLSCR-диодная цепочка

Время роста стрессового напряжения для модели HBM составляет около 10 нс. Когда стрессовое напряжение возникает между шинами питания, напряжение Vx (рис. 5в) растет гораздо медленнее напряжения питания, так как RC-цепочка имеет константу 0,1 – 1 мкс. Благодаря этой задержке инвертор передает на затвор VG высокий уровень сигнала, NCLSCR включается и стрессовый ток проходит через защитное устройство.

При нормальных условиях работы время роста напряжения питания находится в диапазоне миллисекунд, что позволяет поддерживать напряжение на затворе VG = 0 В, то есть защитный элемент выключен. Ток утечки NCLSCR в основном состоит из тока утечки n-МОП транзистора и тока утечки перехода n-карман – p-подложка, которые почти не зависят от температуры. Таким образом, ток утечки такого устройства может быть снижен до очень маленького значения (~1–2 нА) даже при высокой температуре.

Блокирующее напряжение полученного устройства складывается из блокирующего напряжения для диодной цепочки и NCLSCR. Напряжение на управляемом диоде:

, I , I  Ihold, Ihold,

где I - ток через NCLSCR;  - проводимость NCLSCR в низкоомной области; Ihold - ток устройства при вступлении в низкоомную область ВАХ; Vhold - cоответствующее ему напряжение. Тогда общее блокирующее напряжение будет равно: - проводимость NCLSCR в низкоомной области; Ihold - ток устройства при вступлении в низкоомную область ВАХ; Vhold - cоответствующее ему напряжение. Тогда общее блокирующее напряжение будет равно:

Vtotal(I) = VSCR(I) + Vstring(I), I  Ihold. Ihold.

Подставляя сюда известные формулы, получим:

, I , I  Ihold. Ihold.

По этой формуле можно подсчитать необходимое число диодов для того, чтобы блокирующее напряжение превосходило разницу между Vdd и Vcc на нужную величину.

Характеристики NCLSCR-схемы

Диодная цепочка, объединенная с NCLSCR, была протестирована в 0,35-мкм силицидной КМОП-технологии без использования блокировки силицида. Ширина NCLSCR - 80 мкм, длина канала n-МОП - 0,35 мкм, общая площадь - 80x17,5 мкм2. Диод занимает площадь 80x13,2 мкм2. n-МОП, включенный как конденсатор, имеет емкость 2,76 пФ, резистор R1 выполнен в n-кармане и имеет номинал 100 кОм. В табл. 1 и 2 представлены результаты тестирования устройства на выносливость к ESD с различным числом диодов в цепочке и сравнение характеристик разработанного устройства с характеристиками стандартной схемы защиты [4].

Таблица 1. Результаты тестирования устройства на выносливость к ESD с различным числом диодов в цепочке

|

Designs

|

A single NCLSCR

|

NCLSCR +2 diodes

|

NCLSCR +4 diodes

|

NCLSCR +6 diodes

|

NCLSCR +8 diodes

|

NCLSCR +10 diodes

|

|

ESD Level

|

|

HBM ESD Level

|

> 8 KV

|

> 8 KV

|

> 8 KV

|

> 8 KV

|

> 8 KV

|

> 8 KV

|

|

MM ESD Level

|

1600 V

|

1350 V

|

1100 V

|

850 V

|

650 V

|

500 V

|

Таблица 2. Сравнение характеристик разработанного устройства с характеристиками стандартной схемы защиты

|

Perform ance

|

Leakage Current at 3,3 V and 25ºC

|

Leakage Current at 3,3 V and 125ºC

|

HBM ESD Level

|

MM ESD Level

|

ESD Active Area, mm²

|

|

Designs

|

|

Low-Leakage Diode String (NCLSCR + 4 diodes)

|

24,15 pA

|

1,08 nA

|

> 8 KV

|

1100 V

|

80x70,3

|

|

Diode String (6 diodes)

|

4,96 mA

|

1,25 mA

|

> 8 KV

|

500 V

|

80x79,2

|

Схема защиты входных контактных площадок аналоговых устройств с использованием GGNMOST и специальной схемы защиты между шинами питания

Стандартная схема защиты входных контактных площадок цифровых устройств, как правило, состоит из двух элементов, как показано на рис. 6а.

Рисунок 6. Стандартная схема защиты входных контактных площадок от ESD в цифровых устройствах (а); для аналоговых устройств (б); для прецизионных аналоговых приложений (в); путь протекания стрессового тока в случае ESD между двумя контактными площадками (г)

Большая входная емкость и задержка входного сигнала через RC-цепь делают защитные схемы такого типа неприменимыми для аналоговых приложений.

Для защиты входных контактных площадок аналоговых устройств часто используется схема, показанная на рис. 6б.

Эта схема состоит из одного устройства GGNMOST, размеры которого должны быть достаточно большими для обеспечения приемлемого уровня защищенности от ESD.

Увеличение размеров транзистора позволяет повысить локальный потенциал подложки во время ESD, то есть увеличить её сопротивление. Также достаточно большим должно быть расстояние между контактом стока и затвором, чтобы увеличить соответствующее сопротивление и ограничить ток стока во время ESD. Для снижения напряжения срабатывания можно также использовать различные вспомогательные схемы, основанные на технологии связывания затвора с защищаемой контактной площадкой через конденсатор или технологии защелкивания защитного элемента через подложку.

Дополнительно, можно блокировать силицид в области стока GGNMOST, чтобы повысить равномерность протекания стрессового тока в защитном элементе. Но GGNMOST с большими размерами обладает значительной паразитной емкостью, которая напрямую соединена с входной контактной площадкой. Такая паразитная емкость нелинейно зависит от напряжения на входе и неприемлема для прецизионных схем. Нелинейная зависимость входной емкости от входного напряжения приводит к гармоническим искажениям в АЦП и снижает точность. На рис. 6в представлена схема защиты от ESD с низкой входной емкостью и без ограничивающего сопротивления, разработанная для силицидной 0,35-мкм технологии.

Она предназначена для защиты входных контактных площадок прецизионных аналоговых устройств - прецизионных приложений с большим быстродействием.

Описание работы устройства

Диоды Dp1 и Dn1 являются паразитными диодами стоковых областей Mp1 и Mn1. Чтобы уменьшить входную емкость аналоговой контактной площадки, размеры транзисторов Mp1 и Mn1 уменьшены до W/L = 50/0,5 (мкм/мкм). Уровень защиты от ESD по HBM, состоящего из одного GGNMOST с такими размерами, составляет менее 500 В для силицидной 0,35-мкм КМОП-технологии в случае возникновения ESD по PS-режиму (NMOST работает в режиме snapback). Но для NS-режима (паразитный диод стока работает в прямом смещении) этот защитный элемент может выдерживать ESD до 8 кВ для той же технологии.

Чтобы обеспечить высокий уровень защиты от ESD для PD- и ND-режимов, в данной схеме вводится дополнительный элемент защиты между шиной питания и шиной земли. Как видно на рис. 6в, для защелкивания транзистора Mn3 используется RC-цепь, стрессовое напряжение возникает в этой схеме в случае ESD по PS- и ND-режимам. Для PS-режима (ND-режима) стрессовый ток потечет через открытый паразитный диод Dp1 (Dn1) транзистора Mp1 (Mn1), что приведет к включению транзистора Mn3. Транзистор Mn3 специально делается достаточно большим (W/L = 1800/0,5 мкм/мкм) для обеспечения высокого уровня защиты от ESD. Емкость перехода транзистора Mn3 будет велика, но эта емкость не связана с защищаемой контактной площадкой. Это позволяет обеспечить хорошую защищенность контактной площадки от ESD при очень низкой входной емкости.

Для ESD, возникающего между двумя входными контактными площадками, путь протекания стрессового тока показан на рис. 6г.

Согласно тестовым условиям для этого случая, контакты шин питания VDDA и VSSA не зафиксированы. Стрессовый ток сначала течет от защищаемой контактной площадки к шине питания VDDA через открытый паразитный диод Dp1 транзистора Mp1 входной защитной схемы. Таким образом, шина VDDA заряжается стрессовым напряжением. Потенциал шины VSSA близок к потенциалу земли, так как эта шина соединена с заземленной контактной площадкой через диод Dn4 транзистора Mn4 другой входной защитной схемы.

Теперь стрессовое напряжение устанавливается между шиной земли и шиной питания.

Транзистор Mn3, соединяющий эти шины питания, включается с помощью схемы определения ESD, состоящей из RC-цепочки. Стрессовый ток протекает через этот транзистор в шину земли, затем через открытый паразитный диод Dт4 транзистора Mn4 и покидает схему через заземленную контактную площадку. Если правильно подобрать параметры схемы определения ESD, то стрессовый ток может быть быстро выведен из защищаемого устройства. Использование такой схемы защиты обеспечивает полную защиту подзатворного окисла входного дифференциального каскада аналогового устройства без использования последовательного резистора между входной контактной площадкой и защищаемым устройством. Использование данной схемы допускает входной аналоговый сигнал с более широкой полосой пропускания по отношению к аналоговым устройствам со стандартными защитными схемами.

Отдельные диоды в качестве входных защитных элементов будут работать как представленные в данной схеме МОП-транзисторы Mn1 и Mp1. Но транзистор Mn3 обладает некоторым сопротивлением, и не весь стрессовый ток будет течь через защитные диоды. Если стрессовое напряжение будет достаточно большим, подзатворный окисел транзистора дифференциального каскада будет поврежден. Использование транзисторов Mn1 и Mp1 не позволит избежать повреждения, поскольку при вышеназванных условиях они будут работать в snapback-режиме. В этом случае превышение напряжения на контактной площадке ограничено напряжением вхождения в snapback-режим Vsb для этих транзисторов. У короткоканального транзистора Mn1 напряжение вхождения в низкоомную область (~6,5 В) много меньше, чем напряжение лавинного пробоя стоковой области (~8,5 В) для 0,35-мкм КМОП-технологии. Этот запас дает полную защиту подзатворного окисла транзисторов входного каскада аналогового устройства, чего нельзя обеспечить использованием одних диодов. Входная емкость представленной схемы защиты вычисляется как:

Cin = Cpad + Cn + Cp,

где Сpad - это паразитная емкость контактной площадки; Сn

(Сp) - это емкость стоковых переходов области затвор–сток транзисторов Mn1 (Mp1).

Емкости стокового перехода n-МОП и p-МОП транзисторов строго зависят от напряжения на переходе. Входная емкость стандартной схемы защиты сильно изменяется в зависимости от величины входного сигнала. Для представленной схемы входная емкость почти постоянна в диапазоне изменений входного напряжения и равна 1,02 пФ при указанных размерах элементов и размере контактной площадки 96x96 мкм2, причем емкость контактной площадки составляет 0,67 пФ.

Представленная схема защиты аналогового устройства была реализована в силицидной 0,35-мкм КМОП-технологии для защиты инвертирующего и неинвертирующего входов операционного усилителя. Устройство было протестировано по HBM и MM. Результаты тестирования представлены в табл. 3. Критерием отказа устройства является ток утечки 1 мкА при напряжении 5 В на входной контактной площадке после ESD. Устойчивость устройства по отношению к ESD составляет 6 кВ для HBM и 400 В - для MM при любых тестовых условиях.

Таблица 3. Результаты тестирования защитного устройства по HBM- и MM-моделям

|

|

Pin Combination in ESD Test

|

|

PS-mode

|

NS-mode

|

PD-mode

|

ND-mode

|

Pin-to-pin

|

|

HBM, V

|

6000

|

-8000

|

7000

|

-7000

|

6000

|

|

MM, V

|

400

|

-400

|

400

|

-400

|

400

|

Усовершенствованная технология создания биполярного транзистора в КМОП-технологии для диодного включения в схеме ESD-защиты

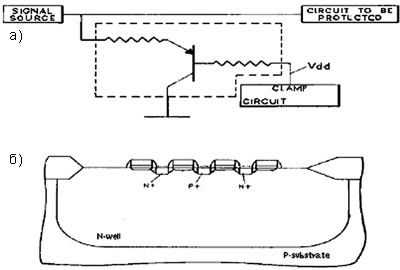

Стандартный вариант диодного включения pnp-транзистора в качестве защитного элемента показан на рис. 7а.

Рисунок 7. Использование биполярного транзистора в диодном включении для защиты от ESD (а); структура биполярного pnp-транзистора в КМОП-технологии (б)

Этот вариант часто используют из-за малой площади и улучшенных свойств по отношению к ESD.

Выполнение биполярного транзистора в КМОП-технологии специально для устройств защиты от ESD было упомянуто в работе [5]. Структура полученного устройства показана на рис. 7б.

Как видно из рисунка, базой транзистора является n-карман, коллектором - p-подложка, эмиттером - p+ диффузия. Область активной базы ограничена шириной поликремниевого затвора.

Литература

- Julian Zhiliang Chen, Ajith Amerasekera, Charvaka Duvvury. Design and Optimization of Gate-Driven NMOS ESD Protection Circuits in Submicron CMOS Processes. IEEE Trans. Electron Devices. Dec. 1998. Vol. 45. P. 2448.

- Ming-Dow Ker, Hun-Hsien Chang, Chung-Yu Wu. A Gate-Coupled PTLSCR/NTLSCR ESD Protection Circuit for Deep-Submicron Low-Voltage CMOS IC’s. IEEE, J. Solid-State Circuits. January 1997. Vol. 32. № 1. P. 38.

- Chau-Neng Wu, Ming-Dow Ker. ESD Protection for Output Pad with Well-Coupled Field-Oxide Device in 0.5-mm CMOS Technology. IEEE, Trans. Electron Devices. March 1997. Vol. 44. № 3.

- Ming-Dow Ker, Wen-Yu Lo. Design on the Low-Leakage Diode String for Using in the Power-Rail ESD Clamp Circuits in a 0.35-mm Silicide CMOS Process. IEEE, J. Solid-State Circuits. April. 2000. Vol. 35. № 4. P. 601.

- Date Jan Willern Noorlag, Warren Robert Anderson. Method for Fabricating a High Performance Vertical Bipolar NPN or PNP Transistor Having Low Base Resistance in Standard CMOS Process. U. S. Patient 5990520. Nov. 1999.

|